Chipsea Technology's PD products have passed Thunderbolt 4 certification and entered the Intel PCL list

The PD chip CS32G052M of Xinhai Technology successfully passed the Thunderbolt 4 certification and entered the Intel Platform Component List (PCL) with its excellent product technical indicators and stable performance. This milestone achievement not only demonstrates the company's deep technical accumulation in the field of PD fast charging, but also marks the company's new breakthrough in the PC ecological layout.

As we all know, Thunderbolt certification is regarded as the highest standard in the PD industry due to its complex and cumbersome certification process. It requires products to reach industry-leading levels in data transmission speed, power transmission efficiency, compatibility, etc. For a long time, this certification has been dominated and controlled by several internationally renowned manufacturers. With the passing of Thunderbolt certification by Chipsea Technology's CS32G052M and its entry into the Intel PCL list, it means that Chipsea's PD products have reached industry-leading standards in data transmission speed, stability, and compatibility.

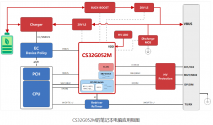

CS32G052M is a single-channel USB Type-C and USB PD controller designed for laptops. It fully complies with the USB PD3.1 standard, supports single-channel independent fast charging, fully ensures charging speed and efficiency, and supports PPS function, which can bring users efficient and safe charging experience. In addition, CS32G052M has multiple protocol data transmission interfaces, supports many fast charging protocols, has a set of SBU Switch, a set of USB2.0 MUX, 12K SRAM and 256K Flash (supports dual-zone allocation), ensuring the stability and security of data transmission, and providing users with more flexible data transmission and control options.

CS32G052M is a single-channel USB Type-C and USB PD controller designed for laptops. It fully complies with the USB PD3.1 standard, supports single-channel independent fast charging, fully ensures charging speed and efficiency, and supports PPS function, which can bring users efficient and safe charging experience. In addition, CS32G052M has multiple protocol data transmission interfaces, supports many fast charging protocols, has a set of SBU Switch, a set of USB2.0 MUX, 12K SRAM and 256K Flash (supports dual-zone allocation), ensuring the stability and security of data transmission, and providing users with more flexible data transmission and control options.