In that case should SMIC revenue skyrocketed?I've discussed this many times before. Each 12-inch wafer can have about 550 chips. If we do 70-75% yield, then that's about 400 chips. Depending on binning criteria, they could do better or worse than that. Again, not all the defective chips are just thrown out.

10 million would take around 25000 wafers. Which isn't all that much really

Huawei needs to produce about 60 million this year and maybe 100 million next year. That would be 150k wafers this year and 250k wafers next. But keep in mind that it's also looking to produce 500k Ascend GPUs and maybe 1.5m Kunpeng CPUs this year. And that number will probably increase 50% next year

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Chinese semiconductor thread II

- Thread starter vincent

- Start date

keep in mind SMSC is a JV. So I think SMIC only gets 40% of the revenue from that IIRCIn that case should SMIC revenue skyrocketed?

AMEC spreading the gospel of the CCP all over the world.

China Microelectronics Corporation has shipped more than 3,000 CCP etching equipment reaction chambers globally.

Recently, the 3000th reaction chamber of the capacitively coupled plasma (CCP) etching equipment of AMEC Semiconductor Equipment (Shanghai) Co., Ltd. (hereinafter referred to as "AMEC") was successfully shipped to an advanced domestic semiconductor chip manufacturer. This important milestone marks that the excellent performance, machine stability and efficient mass production capabilities of AMEC's etching equipment have been widely recognized by customers and the market.

Since the release of the first CCP etching equipment, AMEC has continued to expand its CCP etching equipment product line to meet the increasingly stringent technical needs of advanced chip device manufacturing. The CCP etching equipment series includes single-reaction stage etching equipment Primo SSC AD-RIE®, Primo HD-RIE®, dual-reaction stage etching equipment Primo D-RIE®, Primo AD-RIE® , and integrated etching and glue removal Primo iDEA® . These products provide customers with comprehensive and integrated solutions for a variety of applications from 65nm to 5nm and below. AMEC's etching equipment product line also includes a variety of other inductively coupled low-energy plasma (ICP) etching equipment and through silicon via (TSV) etching equipment. At present, Sinomicron has achieved mass production in more than 700 ICP and TSV equipment in production lines at home and abroad.

Relying on unique technological innovation and differentiated design, AMEC's etching equipment continues to expand its market share and occupies a dominant position in the domestic and foreign semiconductor front-end equipment industry. In 2023, China Micro's operating income will be approximately 6.264 billion yuan, an increase of approximately 1.524 billion yuan compared with 2022, a year-on-year increase of approximately 32.15%. Among them, the sales of etching equipment in 2023 will be approximately 4.703 billion yuan, a year-on-year increase of approximately 49.43%. Previously, etching equipment, which accounted for approximately 75.1% of the company's operating revenue, grew by 55.4% and 57.1% in 2021 and 2022 respectively. The company's total new orders in 2023 will be approximately 8.36 billion yuan, an increase of approximately 2.04 billion yuan from 6.32 billion yuan in 2022, a year-on-year increase of approximately 32.3%, of which new orders for etching equipment will reach 6.95 billion yuan, a year-on-year increase of approximately 60.1%. In addition, China Micro's comprehensive competitive advantages continue to strengthen, and various operating indicators have reached the level of international advanced semiconductor equipment companies. Over the past decade, the company's operating income has continued to grow at an average annual growth rate of more than 35%.

Core Yaohui’s LPDDR4x multiPHY products passed ISO 26262 functional safety product certification

Xin Yaohui Technology Co., Ltd. (hereinafter referred to as "Xin Yaohui") announced that the LPDDR4x multiPHY product successfully passed the ISO 26262 functional safety product certification. This milestone marks Xin Yaohui's products in the field of intelligent driving. Security levels have reached new heights. SGS-CSTC Standards Technical Services Co., Ltd. (hereinafter referred to as "SGS"), an internationally renowned inspection, testing and certification organization, issued the ISO 26262 ASIL-B Ready functional safety product certification to Xin Yaohui. This marks that Core Yaohui LPDDR4x multiPHY has fully complied with the strict specifications of the automotive functional safety standard ISO 26262:2018 ASIL-B level in terms of functional safety architecture design and potential safety risk control caused by random hardware failures.

Ooops you are right. I missed that, sorryisn't 200mm equal 8 inches?

I've discussed this many times before. Each 12-inch wafer can have about 550 chips. If we do 70-75% yield, then that's about 400 chips. Depending on binning criteria, they could do better or worse than that. Again, not all the defective chips are just thrown out.

10 million would take around 25000 wafers. Which isn't all that much really

Huawei needs to produce about 60 million this year and maybe 100 million next year. That would be 150k wafers this year and 250k wafers next. But keep in mind that it's also looking to produce 500k Ascend GPUs and maybe 1.5m Kunpeng CPUs this year. And that number will probably increase 50% next year

I didn't' find any die size of Kunpeng CPU, regarding Ascend I found (from a period when Huawei was still sharing technical specs....long ago) of the previous Ascend 910 on TSMC 7nn. Die size is 182.4 mm2

Recalculating dies per wafer (this time hopefully correctly)

We have 322 DPW, assuming a very pessimistic yield of 40% we get 130 dies per wafer or less than 8K wafers per 1M Ascend 910

Note that I computed the case of Ascend 910, not the new Ascend 920 now in production because I didn't find any die size data on Ascend 920.

So to summarize, 2024 capacity needed is:

Kirin smartphone chips -> 150K wafers in 2024

Ascend AI chips -> 8K wafers in 2024

Let's assume 2 cases for 2024 7nm capacity: 15K wpm (pessimistic) and 25K wpm (optimistic)

Pessimistic case 15K wpm -> 180K wafer / year -> Kirin + Ascend cover 88% of total capacity

Optimistic case 25K wpm -> 300K wafer / year -> Kirin + Ascend cover 53% of total capacity

Even in the pessimistic 15K wpm case SMIC should still have 12% capacity free for other products

I would actually be shocked if Ascend-910B isn't larger than that. Cause most of the die sizes for high end computing chips are at least 400-500mm2. I was expecting 910 to be larger than that. A100 is about 800mm2

Huahong's fab9 has been roofed now

BOE's 63B rmb project in Chengdu has started work. this is its first 8.6 gen production line

Huahong's fab9 has been roofed now

BOE's 63B rmb project in Chengdu has started work. this is its first 8.6 gen production line

Xinsaiwei & Nenghua Semiconductor join forces to write a new chapter

Guangdong Xinsaiwei Technology Co., Ltd. and Jiangsu Nenghua Technology Development Co., Ltd. successfully signed a strategic cooperation agreement, which indicates that the two companies will develop and advance together in the field of power applications in the future. Xinsaiwei and Nenghua Semiconductor are highly complementary in terms of technology platforms, highly consistent in business philosophy, and highly overlapping development directions. Therefore, this cooperation is a natural one and they hit it off immediately!

Chairman and CEO of Guangdong Xinsaiwei Zhi Chunxing (left in the picture) and Zhu Yangang (right in the picture), chairman of Jiangsu Nenghua Semiconductor, successfully signed a strategic cooperation agreement, jointly injecting new momentum into the development of power management applications and power semiconductor devices. Brought new opportunities.

The cooperation between Xinsaiwei and Nenghua is mainly based on power driver chip and gallium nitride device technology to provide customers with a new generation of power management solutions that are more compact, high power density and cost-effective. Xinsaiwei has 15 years of experience in the field of power management, and Nenghua has been researching in the field of gallium nitride for 25 years. Through repeated in-depth discussions and experiments between the two companies, the new Nenghua gallium nitride device is based on Power management chips have also been launched one after another, and have been highly recognized by customers, causing a great response in the market!

Compared with the more common gallium nitride solutions on the market, the solution that combines Xinsaiwei driver and Nenghua gallium nitride technology has lower cost, better reliability, higher production through rate , and has higher requirements for the power supply production environment. Greatly reduced, bringing the possibility of wide-scale promotion and application. At the same time, Xinsaiwei and Nenghua will continue to have higher and deeper technical cooperation, research and development innovation, so that Xinsaiwei can gain more knowledge accumulation in the field of gallium nitride drive, and Nenghua’s gallium nitride devices will also Ushering in rapid development, the two companies have formed a great situation of mutual benefit and win-win cooperation!

Chairman and CEO of Guangdong Xinsaiwei Zhi Chunxing (left in the picture) and Zhu Yangang (right in the picture), chairman of Jiangsu Nenghua Semiconductor, successfully signed a strategic cooperation agreement, jointly injecting new momentum into the development of power management applications and power semiconductor devices. Brought new opportunities.

The cooperation between Xinsaiwei and Nenghua is mainly based on power driver chip and gallium nitride device technology to provide customers with a new generation of power management solutions that are more compact, high power density and cost-effective. Xinsaiwei has 15 years of experience in the field of power management, and Nenghua has been researching in the field of gallium nitride for 25 years. Through repeated in-depth discussions and experiments between the two companies, the new Nenghua gallium nitride device is based on Power management chips have also been launched one after another, and have been highly recognized by customers, causing a great response in the market!

Compared with the more common gallium nitride solutions on the market, the solution that combines Xinsaiwei driver and Nenghua gallium nitride technology has lower cost, better reliability, higher production through rate , and has higher requirements for the power supply production environment. Greatly reduced, bringing the possibility of wide-scale promotion and application. At the same time, Xinsaiwei and Nenghua will continue to have higher and deeper technical cooperation, research and development innovation, so that Xinsaiwei can gain more knowledge accumulation in the field of gallium nitride drive, and Nenghua’s gallium nitride devices will also Ushering in rapid development, the two companies have formed a great situation of mutual benefit and win-win cooperation!

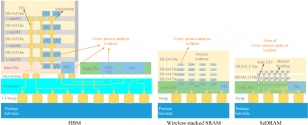

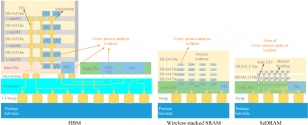

A Cross-Process Signal Integrity Analysis (CPSIA) Method and Design Optimization for Wafer-on-Wafer Stacked DRAM

Institute of Microelectronics of the Chinese Academy of Sciences

School of Integrated Circuits, University of Chinese Academy of Sciences

Xi’an UniIC Semiconductors

A multi-layer stacked Dynamic Random Access Memory (DRAM) platform is introduced to address the memory wall issue. This platform features high-density vertical interconnects established between DRAM units for high-capacity memory and logic units for computation, utilizing Wafer-on-Wafer (WoW) hybrid bonding and mini Through-Silicon Via (TSV) technologies. This 3DIC architecture includes commercial DRAM, logic, and 3DIC manufacturing processes. Their design documents typically come from different foundries, presenting challenges for signal integrity design and analysis. This paper establishes a lumped circuit based on 3DIC physical structure and calculates all values of the lumped elements in the circuit model with the transmission line model. A Cross-Process Signal Integrity Analysis (CPSIA) method is introduced, which integrates three different manufacturing processes by modeling vertical stacking cells and connecting DRAM and logic netlists in one simulation environment. In combination with the dedicated buffer driving method, the CPSIA method is used to analyze 3DIC impacts. Simulation results show that the timing uncertainty introduced by 3DIC crosstalk ranges from 31 ps to 62 ps. This analysis result explains the stable slight variation in the maximum frequency observed in vertically stacked memory arrays from different DRAM layers in the physical testing results, demonstrating the effectiveness of this CPSIA method.

School of Integrated Circuits, University of Chinese Academy of Sciences

Xi’an UniIC Semiconductors

A multi-layer stacked Dynamic Random Access Memory (DRAM) platform is introduced to address the memory wall issue. This platform features high-density vertical interconnects established between DRAM units for high-capacity memory and logic units for computation, utilizing Wafer-on-Wafer (WoW) hybrid bonding and mini Through-Silicon Via (TSV) technologies. This 3DIC architecture includes commercial DRAM, logic, and 3DIC manufacturing processes. Their design documents typically come from different foundries, presenting challenges for signal integrity design and analysis. This paper establishes a lumped circuit based on 3DIC physical structure and calculates all values of the lumped elements in the circuit model with the transmission line model. A Cross-Process Signal Integrity Analysis (CPSIA) method is introduced, which integrates three different manufacturing processes by modeling vertical stacking cells and connecting DRAM and logic netlists in one simulation environment. In combination with the dedicated buffer driving method, the CPSIA method is used to analyze 3DIC impacts. Simulation results show that the timing uncertainty introduced by 3DIC crosstalk ranges from 31 ps to 62 ps. This analysis result explains the stable slight variation in the maximum frequency observed in vertically stacked memory arrays from different DRAM layers in the physical testing results, demonstrating the effectiveness of this CPSIA method.

Conclusions

This paper highlights the distinct nature of WoW 3D multi-layer vertical stacked DRAM Platform SI analysis in terms of cross-process and the absence of process segmentation by I/O circuit. A lumped circuit based on the 3DIC physical structure is introduced to establish a modeling methodology for the vertical stacked DRAM platform. All values of the lumped elements in the circuit model are calculated with the transmission line model. In combination with the dedicated buffer driving method, the CPSIA method is proposed and used for the analysis of 3DIC jitters, integrating DRAM logic and 3DIC designs in a simulation environment, determining the timing uncertainty introduced by 3DIC crosstalk ranging from 31 ps to 62 ps. The silicon results show that the distribution of DRAM_N’s maximum frequency is better than that of DRAM_F, with the average of the tCK_min differences being 26.67 ps, demonstrating the effectiveness of this CPSIA method.

I would actually be shocked if Ascend-910B isn't larger than that. Cause most of the die sizes for high end computing chips are at least 400-500mm2. I was expecting 910 to be larger than that. A100 is about 800mm2

Indeed I realized the usual way is not the right approach for GPU dedicated at AI.

When there are thousand of identical very small core units in a single GPU, as is the case with modern NVIDIA, AMD, Huawei, etc, the actual yield is different.

The point is, manufacturers are able to disable defective cores on the GPU die at packaging time. One extreme case is the Cerebras Wafer Scale unit that is as big as the whole wafer! is shown that Cerebras's yield is always 100% (!)

This is possible because at design time some spare cores / links are reserved and are later used instead of the defective ones that are in some way isolated and disabled (I've read AMD uses electrical fuses to do this).

So let's try another approach!

Under current lithography standards, max die size is and is due to standard photomask of 104mm by 132mm with a 4x reduction when projected on the wafer.

So assume that our hypothetical "Max AI" chip is 26x33 = 858mm2 (if smaller, the number of dies per wafer will be higher so this is a worst case).

Now assume manufacturer can almost always "fix" the chip by disabling defected cores or by binning to lower spec. Assume only in very few cases, where the defects are in very critical no-redundancy positions on the die, we can't recover and have to scrap it. So let's assume a 95% yield (remember Cerebras is 100% using full wafer).

Under these extreme conditions we get 62 dies x 95% yield = 50 dies per wafer

It means that 1M "Max AI" chips would require 20K wafers

This is the worst case and is probably near to where NVIDIA A100 is.

Last edited: