The paper on storage and computing integrated chip of the Institute of Microelectronics was selected for ISSCC 2025 conference

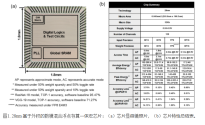

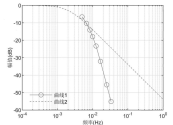

The team led by Researcher Zhang Feng from the National Key Laboratory of Integrated Circuit Manufacturing Technology has designed a transposable approximate and precise dual-mode floating-point storage and calculation integrated macro chip. Through the proposed cyclic weight mapping SRAM scheme, the chip can reuse the multiplication and addition units in forward and reverse propagation, and while realizing the transposition function, it greatly improves the energy efficiency and computing power density compared to the previous transposition storage and calculation integrated macro unit. Through the proposed signed fixed-point mantissa encoding method and vector granularity pre-alignment scheme, the chip realizes the compatibility support of multiple floating-point and fixed-point number systems, and has a smaller precision loss than the traditional coarse-grained floating-point pre-alignment scheme.Through the proposed approximate and precise dual-mode multiplication and addition circuit design, the chip can turn on the approximate mode in the reasoning link with low precision requirements, thereby obtaining a 12% speed increase and a 45% energy consumption reduction, and can turn on the precise mode in the training link with high precision requirements to ensure no precision loss. The storage and calculation integrated macro chip is taped out under the 28nm CMOS process and can support BF16, FP8 floating-point precision operations and INT8, INT4 fixed-point precision operations. The average energy efficiency of BF16 floating-point matrix-matrix-vector calculations reached 48TFLOP/W, and the peak energy efficiency reached 100TFLOPS/W; the average energy efficiency of FP8 floating-point matrix-matrix-vector calculations reached 192.3TFLOP/W, and the peak energy efficiency reached 400TFLOPS/W. This research result provides new ideas for storage-computing integrated architecture chips used for edge training.

The above work was selected for ISSCC 2025 with the title of " A 28nm 192.3TFLOPS/W Accurate/Approximate Dual-mode Transpose Digital 6T-SRAM Compute-in-Memory Macro for Floating-Point Edge Training and Inference ". Yuan Yiyang, a doctoral student at the Institute of Microelectronics, is the first author, and Zhang Feng, a researcher, and Li Xiaoran, an assistant professor at Beijing Institute of Technology, are the corresponding authors. This research result was supported by the Key R&D Program of the Ministry of Science and Technology, the National Natural Science Foundation, and the Strategic Priority Research Program of the Chinese Academy of Sciences.