You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Chinese semiconductor thread II

- Thread starter vincent

- Start date

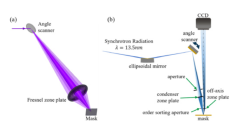

Alternative illumination system for extreme ultraviolet mask inspection based on Fourier synthesis technology.

This study proposes an alternative illuminator based on the Fourier synthesis technology that provides a powerful and flexible way of controlling the coherent properties of illumination for extreme ultraviolet mask inspection. The illuminator achieves coherence control by programming the incident beam scanning a Fresnel zone plate and thus can provide free pupil-fill patterns. In this work, a visible laser-based laboratory microscopic imaging platform has been developed using the illuminator. The spatial resolution and the dense-line image contrast were experimentally evaluated for various coherence factors when a disk and a dipole pupil-fill pattern were applied, respectively. The results are in good agreement with the theoretical calculation of the Rayleigh criterion and the contrast transfer function, which validates the proposed new illuminator. The reliable laser-based imaging platform sheds light on designing and improving EUV mask inspection systems based on synchrotron radiation light sources. The proposed new alternative illuminator will be used in an EUV microscopy at the Shanghai Synchrotron Radiation Facility in future work.

3nm evolving.

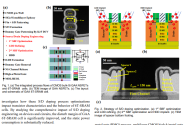

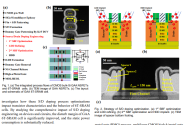

Performance Optimization of Fabricated Nanosheet GAA CMOS Transistors and 6T-SRAM Cells via Source/Drain Doping Engineering.

Abstract:

As gate-all-around nanosheet transistors (GAA NSFETs) replacing current FinFETs for their superior gate control capabilities, it needs various performance optimizations for better transistor and circuit benefits. In this paper, special optimizations to source/drain (S/D) doping engineering including spacer bottom footing (SBF) and refining the lightly doped drain (LDD) implantation process are explored to enhance both fabricated complementary metal oxide semiconductor (CMOS) NSFETs and their 6T-SRAM cells. The experimental results demonstrate that the optimal SBF width increased the static noise margin (SNM) of the SRAM cells by 14.9%, while significantly reducing static power consumption for the balance performance between the NMOS and PMOS and reduced current in all leakage paths of SRAM. Moreover, the LDD optimization significantly reduced off-state leakage current (Ioff) for both NMOS and PMOS due to the reductions of peak electric field in overlap region between the S/D and the channel, leading to a 9.5% improvement in SNM and a substantial reduction in static power consumption. These results indicate that the optimization to S/D doping engineering may achieve substantial performance gains in both the GAA CMOS transistors and the SRAM cells.

Grazing-incidence splicing surface shape measurement method of wafer polishing disk based on expanded beam dynamic interferometer.

Abstract

Aiming at the problem of wafer polishing disk surface measurement in workshop environment, a grazing incidence splicing interferometry measurement method based on beam expansion dynamic interferometer is proposed. This method combines the aspheric beam expansion system and the sub-aperture splicing method to make up for the shortcomings of the dynamic interferometer measurement aperture; the grazing incidence interferometry solves the problem of beam scattering on the rough measured surface, and expands the surface error detection range of the dynamic interferometer. The problem of the defocus change of the system output wavefront is studied. The sub-aperture splicing algorithm based on the self-calibration of the astigmatic aperture effectively eliminates the interference of the system defocus during the sub-aperture splicing process, providing an algorithm guarantee for high-precision sub-aperture splicing measurement. The surface of a wafer polishing disk sample with a diameter of 576 mm is measured and compared with the measurement results of a three-coordinate machine. The average error of the sectional height measurement results of the proposed method is 0.1375 μm, and the flatness error is 0.17 μm. The experimental results show that the proposed method has the ability to detect the surface shape of wafer polishing disks and expands the application range of dynamic interferometers.

Yeah that's my source. He is quite knowledge. Though I haven't communicated with him.

Source-mask co-optimization study for typical EUV design rule patterns with 40nm minimum pitch

Abstract

Source-Mask Co-Optimization (SMO) techniques have significantly supported semiconductor manufacturing quality by enhancing imaging contrast and lithographic process control in advanced lithography nodes over the past decade. Through jointly optimizing the design of the illumination source and modifying the reticle patterns on the mask, the SMO technique has provided a viable method to find the best photo process for a given design rule. In SMO, process parameters such as the Exposure Latitude (EL), the Depth of Focus (DoF), the Mask Error Factor (MEF) can be improved through the definition of a cost function. For EUV, there is an added issue that the optical axis is not normal to the reticle. Although the optical axis is normal to the wafer, there still exists shadowing effect and horizontal-vertical linewidth bias (H-V bias) that needs to be considered. Therefore, in our SMO program, we also put the illumination telecentricity at wafer plane into consideration, which may help reduce pattern shift at defocus positions. In this presentation, we provide an example with a minimum pitch of 40 nm, which is commonly used for the 2~3 nm Back-End-Of-the-Line (BEOL) logic technology nodes. In this example, we will discuss the challenges and potential of our SMO technique and we will offer recommendations for EUV SMO implementations in advanced EUV technology nodes. Our analysis indicates that SMO can continue to improve optimal pattern transfer capabilities by simultaneously optimizing both illumination source and mask design. |

Fast lithographic source optimization adopting RMSProp with iterative shrinkage-thresholding algorithm compressive sensing for high fidelity patterning

Abstract

Fast Source Optimization (SO) is a critical requirement for the 14-5nm node in integrated lithography online technology. Our previous research introduced Bayesian Compressed Sensing SO (CCS-BCS-SO), which effectively delivered high pattern fidelity. However, its processing speed still lags behind that of compressive sensing (CS) SO. This paper introduces the first application of the iterative shrinkage - thresholding algorithm with RMSProp (RMSProp-ISTA) in compressive sensing. This innovation aims to ensure a high-fidelity pattern while improve convergence speed and accelerating SO. The results indicate that the CCS-RMSProp-ISTA-SO method is three times faster than the CCS-BCS-SO method, achieving the fast SO like CS-SO and the high pattern fidelity of SD-SO. |