Peking University has made progress in the field of carbon-based FET biosensors to promote their application in POCT

Field effect transistor (FET) biosensors have significant advantages such as high sensitivity, rapid response and label-free detection, and show great potential in the field of medical point-of-care testing (POCT). FETs based on thin film semiconductor materials have advantages such as good process compatibility and excellent gate control characteristics, so they are highly anticipated in biosensor applications. Semiconductor carbon nanotube (CNT) films have been proven to be ideal channel materials for building high-performance FET biosensors. Although a large number of related research works have been published, they have not yet developed into a true engineering technology. The main reason is that there are key technologies to be solved and the complete technology chain of CNT FET biosensors has not yet been developed, which makes carbon-based biosensor research still limited to the laboratory stage.

Recently, Professor Zhang Zhiyong and Assistant Researcher Xiao Mengmeng from the School of Electronics and the Center for Carbon-Based Electronics Research at Peking University have analyzed from the perspective of practical applications that the complete technical chain of large-scale manufacturing of FET biosensors needs to solve at least two major challenges: (i) developing reliable and scalable manufacturing methods to obtain consistency between batches, and (ii) realizing reliable methods for reading weak signals and portable terminal systems that can read packaged sensor chips. Overcoming these challenges and building a complete technical chain is the basis for promoting the engineering of FET biosensors and, in turn, their application in the field of POCT.

The Peking University team solved the technical difficulties of CNT material preparation, biosensor manufacturing, chip packaging and signal reading point by point, creating a complete chain technology of CNT FET biosensors and developing a solid technical foundation for its application in the field of POCT. Specifically, in terms of material preparation, high-quality and uniform randomly oriented semiconductor CNT films were prepared by improved dip coating technology (Figure 1).

Figure 1: The complete technology chain of CNT FET biosensor

In device preparation, by optimizing the preparation process of CNT FET biosensors, batch preparation of 4-inch wafer carbon-based FETs has been achieved, and the device uniformity has been greatly improved. The coefficient of variation of device performance within the wafer is better than 6%, and the coefficient of variation of device performance between wafers is within 9% (Figures 2 and 3).

Figure 2: Electrical characteristics of CNT FETs fabricated using standard photolithography

Figure 3: Wafer-to-wafer uniformity of CNT FETs

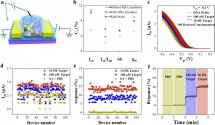

The research team further verified the repeatability of the CNT FET-based ion sensor. At each fixed ion concentration, the standard deviation of the threshold voltage of the tested sensors (100) was within 5.1 mV, which means that the ion concentration information of the solution to be tested can be read by directly testing the drain current of the sensor (Figure 4).

Figure 4: Performance of CNT FET ion sensor

On this basis, the research group developed a standard process for CNT FET biosensor dicing and packaging, and specially developed a dedicated portable device for FET biosensor signal readout, which can realize the plug-and-play of biosensor chips, with a friendly operation interface, and non-professionals can also detect biological targets according to simple instructions. The research group also demonstrated that through this portable and efficient detection system, the detection method and data processing method are optimized, and the CNT FET biosensor can detect biological signals with a concentration as low as 100 aM under a blank background (Figure 5).

Figure 5: Performance of CNT FET biosensor

This work has opened up the complete technical chain of carbon-based FET biosensors, laying a technical foundation for promoting their application in the field of POCT. The relevant results were published online in the journal Nano Letters on August 15 in a paper titled "Mass Production of Carbon Nanotube Transistor Biosensors for Point-of-Care Tests". Liu Haiyang, a 2021 doctoral student at the School of Electronics of Peking University, is the first author of the paper. Assistant Researcher Xiao Mengmeng and Professor Zhang Zhiyong from the School of Electronics of Peking University and the Center for Carbon-Based Electronics Research are co-corresponding authors. Dr. He Jianping from the Hunan Advanced Sensing and Information Technology Innovation Research Institute of Xiangtan University and others participated in this work as co-authors.

This work was supported by the National Key R&D Program of China (No. 2022YFB3204402), the National Natural Science Foundation of China (No. 62225101 and 62174007), and the Micro-Nano Processing Laboratory of Peking University.