The Institute of Microelectronics has made progress in the research field of 3D storage for IGZO DRAM back-end integration.

The rapid development of artificial intelligence has put forward huge demands on hardware resources such as computing and storage, and there is an urgent need to improve the performance and efficiency of memory-level access. At present, the storage system of mainstream computing hardware is composed of on-chip static random access memory (SRAM) and off-chip random dynamic memory (DRAM). Data is transmitted between them through a limited bus, resulting in limited bandwidth, high power consumption and latency. These problems have gradually become a bottleneck for artificial intelligence applications such as big data and high computing power. In addition, the traditional silicon-based six-transistor (6-T) SRAM cell has many limitations in density and energy consumption due to its large feature size and standby leakage problems. At the same time, traditional silicon-based DRAM cells also face problems such as short data retention time and inability to improve storage density through back-end integration. These problems fundamentally limit the power consumption and density of SRAM-DRAM storage systems.

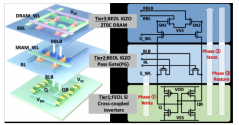

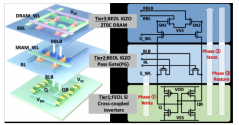

In response to the above problems, the team led by Academician Liu Ming and Researcher Li Ling from the Key Laboratory of Integrated Circuit Manufacturing Technology of the Institute of Microelectronics proposed a new three-dimensional storage structure of IGZO/Si SRAM and IGZO 2T0C DRAM by integrating multi-layer stacked IGZO thin-film transistors (TFTs) with silicon-based circuits, and successfully achieved high-density, low-energy consumption, and high-speed data transmission. In this structure, the IGZO transmission gate is integrated on the front-end silicon-based latch structure, which effectively reduces the occupied space and standby power consumption of SRAM. In addition, based on the vertically stacked three-layer interconnection structure, the lowest delay (<10ns) and lowest energy consumption (2.26fJ) of SRAM-DRAM data transmission are achieved. At the same time, the high data retention characteristics of IGZO 2T0C DRAM enable SRAM to reduce standby power consumption without losing data after a long power outage (>5000s).

The above research results were selected for the 2024 VLSI with the paper titled "First Demonstration of Monolithic Three-dimensional Integration of Ultra-high Density Hybrid IGZO/Si SRAM and IGZO 2T0C DRAM Achieving Record-low Latency (<10ns), Record-low Energy (<10fJ) of Data Transfer and Ultra-long data retention (>5000s)" , and won the Best Demo Paper Award of the conference . This award is only given to two people each year, one each from the process and circuit sub-forums. This work is also the first time that the mainland has won this award. Liu Menggan, Li Zhi and Lu Wendong, doctoral students of the Institute of Microelectronics, are the co-first authors, and Li Ling, a researcher, Yang Guanhua, an associate researcher, and Dou Chunmeng, a researcher of the Institute of Microelectronics, are the corresponding authors.

In response to the above problems, the team led by Academician Liu Ming and Researcher Li Ling from the Key Laboratory of Integrated Circuit Manufacturing Technology of the Institute of Microelectronics proposed a new three-dimensional storage structure of IGZO/Si SRAM and IGZO 2T0C DRAM by integrating multi-layer stacked IGZO thin-film transistors (TFTs) with silicon-based circuits, and successfully achieved high-density, low-energy consumption, and high-speed data transmission. In this structure, the IGZO transmission gate is integrated on the front-end silicon-based latch structure, which effectively reduces the occupied space and standby power consumption of SRAM. In addition, based on the vertically stacked three-layer interconnection structure, the lowest delay (<10ns) and lowest energy consumption (2.26fJ) of SRAM-DRAM data transmission are achieved. At the same time, the high data retention characteristics of IGZO 2T0C DRAM enable SRAM to reduce standby power consumption without losing data after a long power outage (>5000s).

The above research results were selected for the 2024 VLSI with the paper titled "First Demonstration of Monolithic Three-dimensional Integration of Ultra-high Density Hybrid IGZO/Si SRAM and IGZO 2T0C DRAM Achieving Record-low Latency (<10ns), Record-low Energy (<10fJ) of Data Transfer and Ultra-long data retention (>5000s)" , and won the Best Demo Paper Award of the conference . This award is only given to two people each year, one each from the process and circuit sub-forums. This work is also the first time that the mainland has won this award. Liu Menggan, Li Zhi and Lu Wendong, doctoral students of the Institute of Microelectronics, are the co-first authors, and Li Ling, a researcher, Yang Guanhua, an associate researcher, and Dou Chunmeng, a researcher of the Institute of Microelectronics, are the corresponding authors.

Last edited: