You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Chinese semiconductor industry

- Thread starter Hendrik_2000

- Start date

- Status

- Not open for further replies.

No, I just wanted to do an estimation for the total number of transistors based on your density measurement and remembered that number from TechInsights. If it is the measurement from the seal shouldn't it be the number used in calculations like that rather than the outer size. Either way that translates to roughly 11.1 to 11.5 billion transistors. Old kirin 9000 had 15.3 billion transistors. So if your density estimate is correct Huawei must have improved the micro architecture for their cores significantly.bro, you are nit picking. LOL

Die size of 107mm^2 is if measured only from die seal. Full die size would be 110.8mm^2.

"The Hi36A0 GFCV120 die is 10.50 mm × 10.23 mm (die seal) (107.4 mm2) as measured from the die seals, or 10.66 mm × 10.39 mm (110.8 mm2) for the full die"

The generally accepted transistor density calculation is a theoretical density using the below calculation:No, I just wanted to do an estimation for the total number of transistors based on your density measurement and remembered that number from TechInsights. If it is the measurement from the seal shouldn't it be the number used in calculations like that rather than the outer size. Either way that translates to roughly 11.1 to 11.5 billion transistors. Old kirin 9000 had 15.3 billion transistors. So if your density estimate is correct Huawei must have improved the micro architecture for their cores significantly.

0.6 x (NAND2 Transistor Count)/(NAND Cell Area) + 0.4 x (Scan Flip Flop Transistor Count)/(Scan Flip Flop Cell Area).

This is used for simple benchmarking between different process.

In reality, chip designers may not use exact 0.6/0.4 split between NAND and Logic cells. So use the transistor density number as a relative comparison purpose only. You won't be able to accurately derive the acutal # of transistor on an actual chip with transistor density and the chip area.

I added info for tsmc 5nm. Despite many sources that indicated Kirin9000S is not as good as Kirin9000 in term of Performance & Power consumption, there were still a few on SDF that continued to mistakenly claim otherwise. Below table should clarify why Kirin9000 built on a 5nm process is expected to do better on PP portion of PPA than Kirin9000S.For those interested in analysis of technical data, please read on, otherwise you can skip this post.

I just read the latest TechInsight report on teardown of Kirin9000s. It looks like the chip is just a tad worse than I had thought. Many on social media had assumed this chip to be similar to tsmc 7nm+ with transistor density of 114ish MTx/mm^2. But the dimension on Kirin9000s with SMIC N+2 is a bit larger, so the cell area would be larger, and thus lower transistor density than tsmc 7+nm process..

Some critical dimensions measured and provided by TechInsight:

- Hi36A0 GFCV120 die size: 10.66 x 10.39 mm (110.8 mm^2)

- fin pitch: 33nm

- CPP: 63nm w/ SDB

- M2: 42nm

- Standard Cell height: 252nm (6-track)

How does this compared to N+1 & tsmc 7nm+?

tsmc 7nm+ SMIC N+2 tsmc 7nm N+1 fin pitch 30nm 33nm 30nm 37nm CPP 57nm w/ SDB 63nm w/ SDB 57nm w/ DDB 63nm w/ SDB M2 40nm 42nm 40nm 44nm cell height 240nm 252nm 240nm 264nm M Tx/mm^2 113.9 est. <104 96.5 89

I had previously indicated N+2 process would be better than tsmc 7nm but worse than tsmc 7nm+. But the Metal2 (M2) dimension on SMIC N+2 based on TechInsight's analysis is 5% larger than my assumption. The N+2 Contact Poly Pitch (CPP) is also 5% larger than my assumption. Taken CD sizes provided by TechInsight, the cell area would reduce and Transistor density increase by ~15% from N+1. So rough estimate, N+2 would have Trasistor density of ~104M Tx/mm^2 ish. Not exactly at tsmc 7nm+ level, but close enough.

Anyhow, this is comparison of SMIC's process capabilities in terms of PPACt on a transistor level. N+2 will be slightly inferior to tsmc 7nm+ in terms of Performance, Power consumption, Area, and perhaps cost. Slight improvements or differentiations could still be made through optimization of chip design (e.g. better designed chip with N+2/104 MT/mm^2 process may yield similar performance as a typical design on tsmc 7nm+/113.9 MT/mm^2). But fundamentally, you will not expect the N+2 to reach the level of tsmc 5nm which would have better PPACt due to smaller dimensions, higher transistor density, etc.

Note: all info except SMIC N+2 above could be found and verified on websites like wikichip.org; semiwiki.com, and even articles. info for N+2 I obtained through TechInsight's report.

Performance: Kirin9000S has lower clock speed than 9000

Power: Kirin9000S necessitate bigger heat dissipation than Kirin9000

| tsmc 5nm (EUV) | tsmc 7nm+ (EUV) | SMIC N+2 | tsmc 7nm | SMIC N+1 | |

| fin pitch | 25nm | 30nm | 33nm | 30nm | 37nm |

| Contact Poly Pitch | 50nm | 57nm w/ SDB | 63nm w/ SDB | 57nm w/ DDB | 63nm w/ SDB |

| Metal 2 | 30nm | 40nm | 42nm | 40nm | 44nm |

| cell height | 180nm | 240nm | 252nm | 240nm | 264nm |

| M Tx/mm^2 | 138.2 | 113.9 | est. <104 | 96.5 | 89 |

| Kirin 9000 | Kirin 9000S |

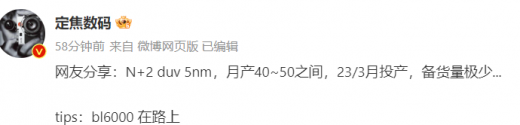

According to his comment in this post, yield is above 60%...5nm N+2 DUV process...they just produced from 23/3... monthly output is 40-50....

View attachment 118378

Why was Huawei using Sk hynix NAND instead of YMTC in the 1st place?Once Huawei finishes their stock of SK Hynix NAND, they will switch over to YMTC.

YMTC started to mass produce 300+ layer NAND. From a reputable source.

I assumed 50 wafer per month.5nm N+2 DUV process...they just produced from 23/3... monthly output is 40-50....

View attachment 118378

50 * 300 = 15,000 kirin 9100 per month.

Source?YMTC started to mass produce 300+ layer NAND. From a reputable source.

I forgot which post.Source?

- Status

- Not open for further replies.