GAA transistor manufacturing process using ALD tools and Naura etching tools.

A Novel Si Nanosheet Channel Release Process for the Fabrication of Gate-All-Around Transistors and Its Mechanism Investigation.

Abstract

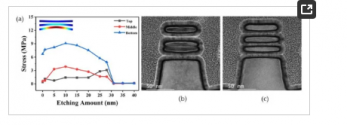

The effect of the source/drain compressive stress on the mechanical stability of stacked Si nanosheets (NS) during the process of channel release has been investigated. The stress of the nanosheets in the stacking direction increased first and then decreased during the process of channel release by technology computer-aided design (TCAD) simulation. The finite element simulation showed that the stress caused serious deformation of the nanosheets, which was also confirmed by the experiment. This study proposed a novel channel release process that utilized multi-step etching to remove the sacrificial SiGe layers instead of conventional single-step etching. By gradually releasing the stress of the SiGe layer on the nanosheets, the stress difference in the stacking direction before and after the last step of etching was significantly reduced, thus achieving equally spaced stacked nanosheets. In addition, the plasma-free oxidation treatment was introduced in the multi-step etching process to realize an outstanding selectivity of 168:1 for Si0.7Ge0.3 versus Si. The proposed novel process could realize the channel release of nanosheets with a multi-width from 30 nm to 80 nm with little Si loss, unlocking the full potential of gate-all-around (GAA) technology for digital, analog, and radio-frequency (RF) circuit applications.

2. Materials and Methods

The main fabrication process flow of vertically stacked horizontal nanosheets is shown in Figure 1a. First, three cycles of the Si/SiGe multilayer were deposited on an eight-inch Si substrate using a reduced pressure chemical vapor deposition (RPCVD) apparatus, where the thickness of the Si and SiGe layers was around 9 nm, and the Ge composition in the SiGe layers was 30% (the Si/SiGe multilayer wafer used in this paper was a commercially available wafer). Then, a hard mask was grown on the Si/SiGe multilayer, and the designed test pattern was transferred to the hard mask. The designed test pattern was transferred to the Si/SiGe multilayer structure by anisotropic etching using the inductively coupled plasma (ICP) machine. Next, the hard mask was removed by wet etching using a 1% hydrofluoric acid solution, while the native oxide was removed. After that, the sacrificial SiGe layers of the channel were removed by isotropic etching,

using the remote plasma dry etching apparatus (NAURA HSE200C) to form the suspended vertically stacked Si nanosheets. Finally, the high K dielectric and metal gate (HKMG) were uniformly wrapped on the nanosheets by atomic layer deposition (ALD) technology. The cross-section of the channel was analyzed by a high-resolution transmission electron microscope (TEM) to check the mechanical stability of the stacked nanosheets.