What you are saying is true only if EUV could be used with single patterning but because of multiple issues, tsmc is already on EUV double patterning. 2150i should be able to do 4 nm process.

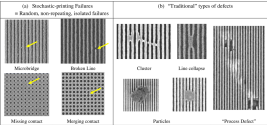

TSMC uses EUV double patterning because there are lots of features they need to pattern smaller than EUV’s minimal line width for 3 nm and below. Anything that requires 2 steps for EUV requires 4-6 steps with DUVi so no, no matter how much extra patterning you have to do with EUV you are saving a lot of steps relative to DUVi. The tradeoff is really over whether you can afford a feature to have higher line roughness, and whether the specific feature can be practically repaired after initial deposition and etching steps since that’s what the EUV stochastic noise issues are primarily affecting.

One way to square the difference between our inferences and the claims here is that even if all the auxiliary ecosystem for a full EUV process is ready they all need some time to work out teething issues to reach a level of certification sufficient for mass deployment. You can use EUV for production and also not be confident enough with the process to deploy at scale. And if I had to guess that’s where I think we are at.I dont think you have been following this thread. One the reason I said from a couple years that China has already has EUV machines is because all the ecosystem that has been develop around it. From EUV mask inspection tools, EUV metrology tools, to EUV photoresists, pellicle development and so on. None of that can happen in vacuum (no pun intended), my guess is that the EUV tooling and anchilliary ecosystem in China have is as advanced as whatever EUV lithography machine they have. The ecosystem is going neck to neck with the main tool.

Last edited: