50k wpm is a lot

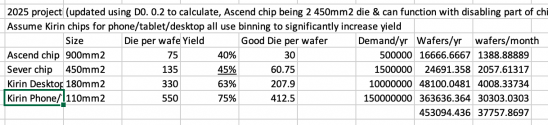

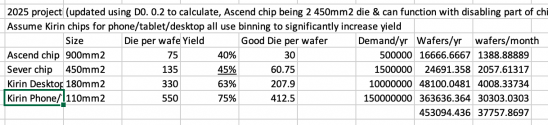

Doing some rough calculation here. I think 500k Ascend chips is a lot. I did some calculation assuming they are making Ascend-920 (and computation increases to 600 TFLOPS FP16), that'd be 300 EFLOPS a year, which is way more than what they are adding right now

Server chips being 3x that seems reasonable

10 million desktop a year would easily dominate the market (I maybe overestimating things there)

The biggest load (by far) are the kirin chips for phones and tablets and possibly the new vision pro products.

I put down 150 million for all of that, which again is a very high number. That resulted in 30k wpm for the kirin SoCs

if they can get to 50k wpm, they can supply chips to other OEMs also.

50k wpm even if we assume 400 chips per wafer is 240 million per year.

to support the entire Chinese phone OEM market, you need about 100k wpm

Doing some rough calculation here. I think 500k Ascend chips is a lot. I did some calculation assuming they are making Ascend-920 (and computation increases to 600 TFLOPS FP16), that'd be 300 EFLOPS a year, which is way more than what they are adding right now

Server chips being 3x that seems reasonable

10 million desktop a year would easily dominate the market (I maybe overestimating things there)

The biggest load (by far) are the kirin chips for phones and tablets and possibly the new vision pro products.

I put down 150 million for all of that, which again is a very high number. That resulted in 30k wpm for the kirin SoCs

if they can get to 50k wpm, they can supply chips to other OEMs also.

50k wpm even if we assume 400 chips per wafer is 240 million per year.

to support the entire Chinese phone OEM market, you need about 100k wpm