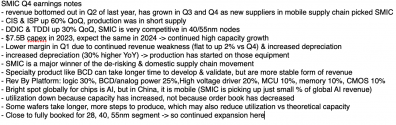

Huanghu Test received 100 million yuan in Series B financing and has focused on DRAM memory testing for more than 30 years

Huanghu Test Technology (Shenzhen) Co., Ltd. (referred to as: Huanghu Test) completed a round B financing of 100 million yuan, led by CICC Capital, Wanlian Guangsheng, Xincong Yuanchen, Ruifa Fund, etc. participated in the investment, and the old shareholder Wanwuyi made additional investment.

Official news from Huanghu Test shows that it has focused on the field of memory high-speed test equipment for more than 30 years and is a world-renowned and industry-recognized manufacturer of memory high-speed FT test equipment. The core technical team members have focused on this field for more than 20 years. At the beginning of 2020, the core team of Huanghu Testing returned to China for development. Company founder Lai Junsheng has been engaged in the research and development of DRAM memory test equipment for more than 30 years, and the core team's memory test research and development experience averages more than 20 years.

According to Shenzhen Hi-tech Investment, in early 2020, Huanghu Test established a DRAM testing equipment R&D center and testing service center in Shenzhen. Huanghu Test has focused on the field of DRAM memory testing for more than 30 years. It is a world-renowned memory test equipment manufacturer and test solution supplier. Its customers are all over the world, including major memory chip manufacturers, memory stick manufacturers, servers and high-end system manufacturers. It has 100 % Test equipment and intellectual property rights for accelerated aging and memory fault-tolerant repair technology . Royal Tiger Testing is committed to establishing China's memory testing standards, developing independently controllable, internationally leading memory testing equipment, and setting a new technological benchmark in the industry.