This is the information that I have found about the possibility of a 5nm node using 193nm immersion.

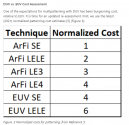

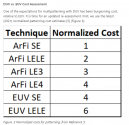

in 2019 the Shanghai ICRD released this about the possibility of a 5nm node, due stochastic EUV was not intended to be used in the FEOL <at least in this paper> due the need of high resolution pitches but the intended to be use in the metal pitches of the BEOL for what is considered at the time to be an "economical" double patterning LELE.

But is really economical?

the cost of DP EUV are higher than QP DUVi.

In the paper the main issue is overlay accuracy but if you can't get good overlay you can't pattern layers with EUV either. An overlay can be worked with external tools and algorithms.

in 2023 again overlay and etching are still the main issue.

Naura and AMEC are developing more advanced etching tools.

AMEC is developing an cryogenic etching tools that could allow to etch finer HAR patterns.

Naura etching tools have already been used for a 5nm SAQP research.

this is from 2020.

in 2019 the Shanghai ICRD released this about the possibility of a 5nm node, due stochastic EUV was not intended to be used in the FEOL <at least in this paper> due the need of high resolution pitches but the intended to be use in the metal pitches of the BEOL for what is considered at the time to be an "economical" double patterning LELE.

But is really economical?

the cost of DP EUV are higher than QP DUVi.

In the paper the main issue is overlay accuracy but if you can't get good overlay you can't pattern layers with EUV either. An overlay can be worked with external tools and algorithms.

in 2023 again overlay and etching are still the main issue.

Naura and AMEC are developing more advanced etching tools.

AMEC is developing an cryogenic etching tools that could allow to etch finer HAR patterns.

Naura etching tools have already been used for a 5nm SAQP research.

this is from 2020.