You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Chinese semiconductor thread II

- Thread starter vincent

- Start date

Bro I think the reason why SMEE will not announce the official launching of SSA 800A Duvi, They want the American to pursue more sanction to hasten its semiconductor development, in detrimental for ASML.you guys seriously think. China will stop if lets suppose USA lift off all the sanctions ... absolutely no chance. ship has sailed.

strict orders from above, no matter what, China has to achieve self-sufficiency in all core technologies. and we are very close to our goal.

So Sir A big possibility that SMIC maybe producing N+4 3nm chip ahead of TSMC (5nm) and Intel (7nm) Arizona FAB by 2027.

3 months ago, I posted that Huawei is building another IC factory that will be completed in 2026...So Sir A big possibility that SMIC maybe producing N+4 3nm chip ahead of TSMC (5nm) and Intel (7nm) Arizona FAB by 2027.

Using SSA800A Duvi or an EUVL or both? the timeline for the completion of the FAB coincide with the possible mass production of a commercial EUVL.3 months ago, I posted that Huawei is building another IC factory that will be completed in 2026...

Thanks for translation.

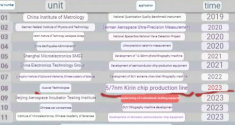

To me the most interesting part is the blue one at the top

Harbin Institute won the prize for their ultra precise wafer stage with top speed (translates in productivity) and top positioning error of just 0.1nm(!!!!) although not clear what "dynamic calibration" actually means. I don't think it is overlay accuracy.

They say they closed the gap with ASML in wafer stage positioning, this is a big claim!

Wafer stage positioning is a key enabler for 7/5nm nodes with a DUVi machine.

HIT post basically confirms their progress not in SMEE's 14/28nm DUVi projects, but also CIOMP's EUV work, production of 5/7nm Kirin chips, CETC SMEs and CAS SMEs. Basically, it got awarded for being part of most of the major semi projects from past 2/3 years

The ascend 920 post is pretty amazing too. I'm dubious of some of the claims in their like the chip-to-chip interconnect.

but i would not be surprised if its computation power is 1000 PFLOPS FP16. one of the well known issues with Ascend-910B is the chip to chip performance

Even aside from the headline numbers, it suggest Ascend-920 consumes less power, has better computation across the board than H100

Has better chiplet technology, more HBM memory

I find the HIT post to be more believable than Ascend post

The ascend 920 post is pretty amazing too. I'm dubious of some of the claims in their like the chip-to-chip interconnect.

but i would not be surprised if its computation power is 1000 PFLOPS FP16. one of the well known issues with Ascend-910B is the chip to chip performance

Even aside from the headline numbers, it suggest Ascend-920 consumes less power, has better computation across the board than H100

Has better chiplet technology, more HBM memory

I find the HIT post to be more believable than Ascend post

Last edited:

MMO and SMO will depend more on the holistic solution that SMEE and others will provide.Thanks for translation.

To me the most interesting part is the blue one at the top

View attachment 127707

Harbin Institute won the prize for their ultra precise wafer stage with top speed (translates in productivity) and top positioning error of just 0.1nm(!!!!) although not clear what "dynamic calibration" actually means. I don't think it is overlay accuracy.

They say they closed the gap with ASML in wafer stage positioning, this is a big claim!

Wafer stage positioning is a key enabler for 7/5nm nodes with a DUVi machine.

That will depend on:

-The grating and interforemeter positioning sensors accuracy in both in the wafer stage and in the reticle stage.

-Overlay Mark Measurement Alignment accuracy:

Chinese semiconductor industry

“We need different tools,” she told a Senate Commerce Committee hearing. “We need additional resources around enforcement.” That's what all bureaucrats always say: "we need more resources and more power because what we do is critical". No bureaucrat will ever admit that what they do is...

www.sinodefenceforum.com

Chinese semiconductor industry

Research on wafer stage overlay-μDBO(micro Diffraction Based Overlay) targets by lithography imaging simulation software 1. Front-end System and Integration Engineering Department, Shanghai Micro Electronics Equipment Group Co., Ltd.,(SMEE) Shanghai 201203, China; 2. Metrology Equipment...

www.sinodefenceforum.com

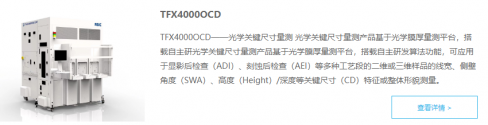

-Metrology tools:

Overlay Metrology tools.

CDSEM tools

Inspection tools:

AEI and ADI

Computational lithography software.