You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Chinese semiconductor industry

- Thread starter Hendrik_2000

- Start date

- Status

- Not open for further replies.

No doubt on the importance of Ascend chip. I did not even bring up the profit margin of either products in my previous post. I'd still be happy even if Huawei is selling Ascend at a loss just to keep the product and the team alive. I was only questioning whether the cost comparison being fair.

the R&D cost are sunk. denying profit to US, while building up human capital in china is more important at this stage.

with the profit margin that nvidia chips are having, it is not difficult to make a small profit while undercutting it in price.

I'm sure SMIC N+3 had been mentioned somewhere on the internet by someone before.@hvpc this is the first time that I read about SMIC N+3. I just searched the net but absolutely no info on this.

Can you share a bit more about SMIC N+3? Is there any public info on this? Or is something you know from your insider info?

I can't share actual CPP & MMP size, but I will tell you that the SMIC N+2 & N+3 feature sizes straddle that of tsmc 7nm. For example, the minimum metal pitch (MMP) of SMIC N+2 is 5% larger and N+3 is 5% smaller than tsmc 7nm. N+3 MMP is more than 20% larger than tsmc 5nm, so any speculation or claims that N+3 is 5nm is way off from the truth.

there's a lot 'best guess' at what these critical feature CD pitch for major fabs & each of their process nodes. You could google these to get an idea roughly what CD pitch per nodes per fabs are. Here's one of the source you could reference for 7nm process node:

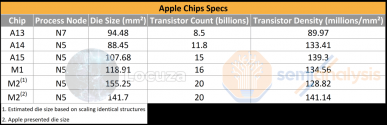

if N+2 is around 115-120 MTr/mm^2 (120 is what some Chinese sources are claiming, so a little less than N7+), then adding another 20+% in density (N+1 to N+2 was > 25%) would get us to 140-145MTr/mm^2. That's basically Samsung 4LPP or betterI'm sure SMIC N+3 had been mentioned somewhere on the internet by someone before.

I can't share actual CPP & MMP size, but I will tell you that the SMIC N+2 & N+3 feature sizes straddle that of tsmc 7nm. For example, the minimum metal pitch (MMP) of SMIC N+2 is 5% larger and N+3 is 5% smaller than tsmc 7nm. N+3 MMP is more than 20% larger than tsmc 5nm, so any speculation or claims that N+3 is 5nm is way off from the truth.

there's a lot 'best guess' at what these critical feature CD pitch for major fabs & each of their process nodes. You could google these to get an idea roughly what CD pitch per nodes per fabs are. Here's one of the source you could reference for 7nm process node:

That would seem to be sufficient transistor density to match A15 & M1

and about same as Kirin-9000

Last edited:

that list is incomplete and hence incorrect.I thought for sure HLMC got 1980i before

Something feels off about this.

HLMC had multiple 1980 and multiple 2050 last year.

SMIC SN2 always had enough litho tools to reach 35K wpm. The reason they've been limited to 20K wpm is due to lack of American process equipment. No domestic substitute exist that could support de-americanization of 7nm process tools at the moment.Now, let's assume this is accurate and they essentially doubled the number of advanced Arfi scanners they have.

If what they had before is sufficient for 35k wpm (8 scanner is probably not enough for that, but I assume they have some 1970i & 1965i also)

then what they have now allows them to get the 35k wpm with SN2

@hvpc does this sound about right to you? Interesting they got that many 2000i

But it is now clear that rather than splitting the market to slow down Americans, China is more interesting in coming for the whole thing, so it is outsourcing the competition against US state giants to private actors, keeping the global market intact.

Yeah, agree, that was the logical outcome of this, if or when DUVi or EUV appears in China. We could see it coming a mile away.

Which tools are still missing.that list is incomplete and hence incorrect.

HLMC had multiple 1980 and multiple 2050 last year.

SMIC SN2 always had enough litho tools to reach 35K wpm. The reason they've been limited to 20K wpm is due to lack of American process equipment. No domestic substitute exist that could support de-americanization of 7nm process tools at the moment.

if N+2 is around 115-120 MTr/mm^2 (120 is what some Chinese sources are claiming, so a little less than N7+), then adding another 20+% in density (N+1 to N+2 was > 25%) would get us to 140-145MTr/mm^2. That's basically Samsung 4LPP or better

View attachment 118300

That would seem to be sufficient transistor density to match A15 & M1

View attachment 118301

and about same as Kirin-9000

That is what I believe, after reading these reports, and comparing numbers.

This is the world's best 7nm chip.

It almost reaches 5nm performance!

That brings up an interesting commercial scenario, it that if China Inc. had a choice between using a 5nm chip from TSMC or this 7nm Kirin chip, and since they are roughly comparable, why bother with the 5nm chip, when it will cost more?

They won't bother with it.

Therefore, this 7nm is here to stay for a while.

Therefore, this report EUV project in China, is mainly geared to make the 3nm chip or 2nm chip or 1nm chip if possible. They could skip the 5nm chip with this 7nm Kirin9000S chip.

No wonder the Chinese are angry about this chip war. They spent so much money, just to make a 3nm chip?

If that is the case, they will want a little more of a pound of flesh out of this fight.

That is what I believe, after reading these reports, and comparing numbers.

This is the world's best 7nm chip.

It almost reaches 5nm performance!

That brings up an interesting commercial scenario, it that if China Inc. had a choice between using a 5nm chip from TSMC or this 7nm Kirin chip, and since they are roughly comparable, why bother with the 5nm chip, when it will cost more?

They won't bother with it.

Therefore, this 7nm is here to stay for a while.

Therefore, this report EUV project in China, is mainly geared to make the 3nm chip or 2nm chip or 1nm chip if possible.

No wonder the Chinese are angry about this chip war. They spent so much money, just to make a 3nm chip?

If that is the case, they will want a little more of a pound of flesh out of this fight.

I see this more as an intermediary measure, the WS-10C to the WS-15 that’s the 5nm chip. The important thing now is to breakthrough the sanction barrier and allow mass production of the chip so that Huawei has the capital and experience to become a world beater again.

well, I think what we believe doesn't matter. What the reality is matters.That is what I believe, after reading these reports, and comparing numbers.

This is the world's best 7nm chip.

It almost reaches 5nm performance!

That brings up an interesting commercial scenario, it that if China Inc. had a choice between using a 5nm chip from TSMC or this 7nm Kirin chip, and since they are roughly comparable, why bother with the 5nm chip, when it will cost more?

They won't bother with it.

Therefore, this 7nm is here to stay for a while.

Therefore, this report EUV project in China, is mainly geared to make the 3nm chip or 2nm chip or 1nm chip if possible. They could skip the 5nm chip with this 7nm Kirin9000S chip.

No wonder the Chinese are angry about this chip war. They spent so much money, just to make a 3nm chip?

If that is the case, they will want a little more of a pound of flesh out of this fight.

a lot of the netizen claims are very optimistic. We will find out when the time comes how much improvement SMIC can make. Getting yield up isn't easy and SMIC is limited in tools it can use.

I really don't think the choice is between TSMC 5nm vs Kirin chip here. At end of the day, SMIC is very capacity/tools limited.

We've seen a lot of optimistic stuff from AMEC/NAURA recently, but those tools need time for validation. Maybe in 6 months, SMSC will be expanding again past the 20k limit that @hvpc refers to, but that all depends on SMIC actually completing validation of domestic equipments. It is a good thing they have a lot of ASML lithography still, because that overcomes a lot of other issues

As I said before, they need not 25k wpm of Finfet, they need at least 125k. Probably more like 200k. And a lot of more memory chip capacity to satisfy domestic demands. We are still in year 1 post October sanctions. Even in optimistic case (which means EUV prototype available), we are still 2 years from taking a real breather and 5 years from being able to mostly take care of domestic needs on logic side.

Memory chip side is a whole different and equally challenging ball game

- Status

- Not open for further replies.