We anticipate a drop BUT not this bad!!!! With weaker demand on its 7nm chips and the challenges from SMIC 14nm against their 16nm, only the 5nm is their major revenue generator as their savior the 3nm is having problem attracting customers due to high production cost.

TSMC Cuts Down Orders By Up to 50%, Sending Shockwaves Says Report

Nov 1, 2022, 03:11 PM EDT

FILE PHOTO: The logo of Taiwan Semiconductor Manufacturing Co (TSMC) is pictured at its headquarters, in Hsinchu, Taiwan, Jan. 19, 2021. REUTERS/Ann Wang

This is not investment advice. The author has no position in any of the stocks mentioned. Wccftech.com has a

The Taiwan Semiconductor Manufacturing Company (TSMC) has cut down its orders to suppliers according to reports in the Taiwanese press. TSMC, which is facing an industry slowdown as its customers struggle with demand slowdown, cut down capital expenditures for 2022 earlier this year, and the firm cited a lack of demand forecasting as the primary reason behind the drawdown.

Now, the firm is also rumored to have significantly reduced its 3-nanometer output estimates for this year, in the latest bit of speculation surrounding the advanced chip manufacturing technology scheduled to enter production in the current quarter.

TSMC's 3-nanometer Average Monthly Production To Drop By 77% Says Report

comes courtesy of the United Daily News (UDN) and it speculates that TSMC has started to cut down its supplier orders. These orders form the backend, or upstream, of the semiconductor manufacturing supply chain, and they involve a variety of products such as TSMC procuring silicon wafers and other consumable to keep its machines running.

UDN's sources believe that TSMC has reduced these orders by as much as 50%, with the drop coming after the fab also cut down its spending. Due to the critical nature of the company as Taiwan's largest and leading chipmaker, the order cutdown has also sent shockwaves down the chip sector as a whole.

TSMC, and the chip sector has also been facing inventory corrections this year, and the company expects these conditions to persist and potentially peak during the first quarter of next year. The chipmaker has however seen strong demand for its leading edge 3-nanometer technology, with its chief

that the tape-outs for 3nm are more than double than the ones TSMC received for earlier technologies. In the chipmaking industry, tape-out refers to the finalized design from companies such as AMD which is sent to the chipmaker so that the latter can tailor its equipment to the product.

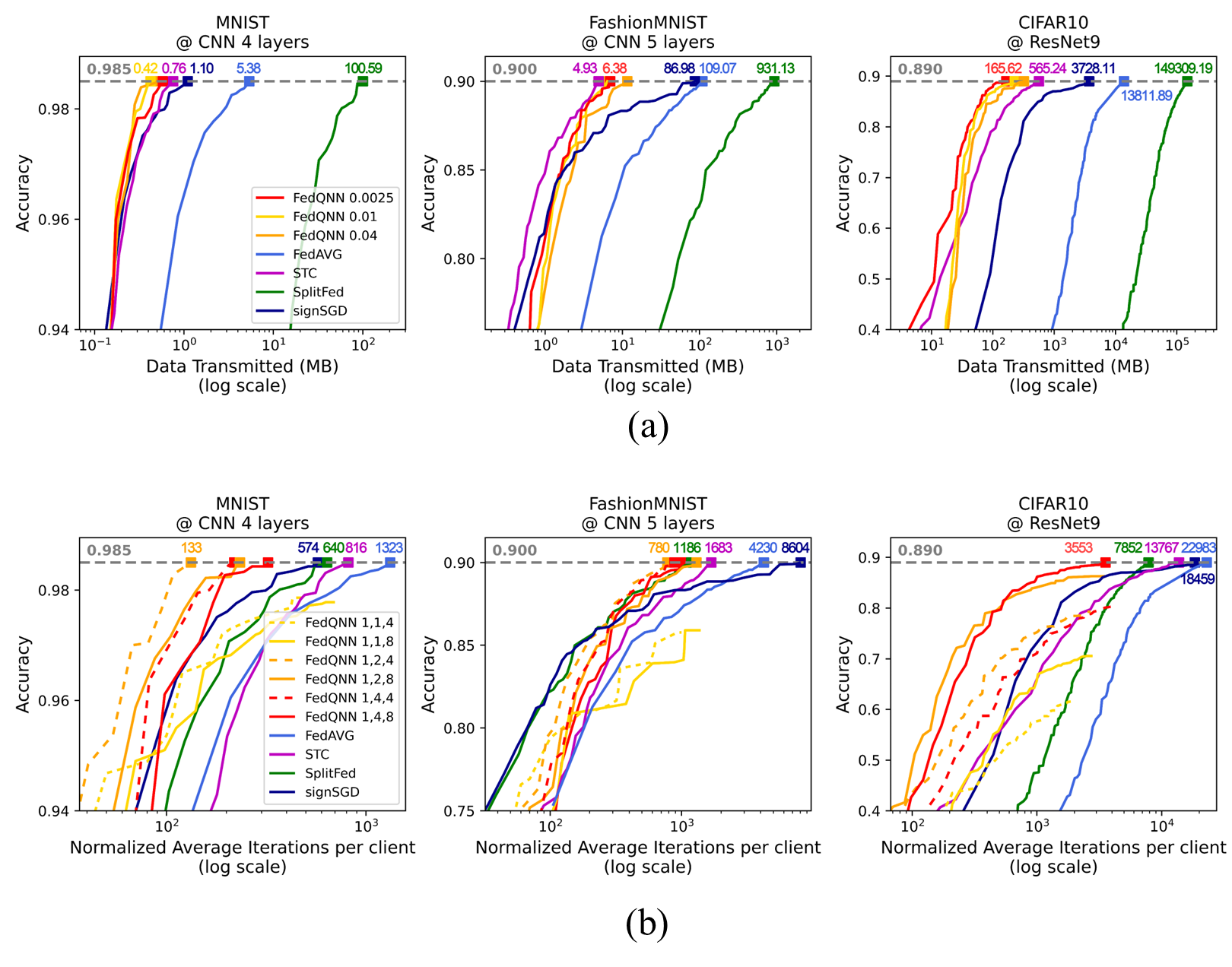

TSMC's third quarter of 2022 earnings report revealed that while revenue contribution from older technologies fell, its latest 5-nanometer products managed to grow. Image: TSMC

According to TSMC's suppliers, the order flow started to weaken in the previous quarter, and this has continued into the current quarter and into the first quarter of next year as well. TSMC shared during its latest earnings report that it is facing difficulty in procuring chipmaking equipment, especially to keep up with its customer orders, and that this when combined with an industry slowdown is forcing the firm to reduce spending.

On the topic of 3-nanometer, the picture painted by UDN is not great either. Its sources suggest that the monthly average output for the new technology was slated to sit at 44,000 wafers previously, and this has now dropped by a whopping 34,000 wafers to now sit at 10,000 wafers for a 77% drop. Key reasons behind this drop are reduced orders from both Apple and Intel - with Intel's own technology also facing delays and Apple choosing to launch its M2 personal computers in March. These imply that TSMC will not be making any chips for Apple this year, and since Intel itself is also facing delays, its products which use some of TSMC's chips will also see orders flow in later.

Today's report is the latest bit in a gloomy outlook for the chip sector, which was one of the best performing industries as earlier as last year as a massive influx of orders in the wake of the coronavirus pandemic and the auto industry led to more orders than the chipmakers could absorb.