With the rapid development of information technology, the demand for high-performance and low-power microprocessors continues to grow. Traditional silicon-based semiconductor technologies have encountered numerous bottlenecks in performance enhancement, such as drain-induced barrier lowering, reduced mobility caused by interface scattering, and limited current on/off ratios. These limitations have spurred researchers to seek out new materials. Two-dimensional (2D) semiconductors have emerged as a promising solution due to their atomic thickness, excellent electrical properties, and mechanical flexibility[1−5]. Despite significant progress in the wafer-scale growth and device fabrication of 2D materials, integrating them into large-scale functional circuits remains a challenge[6−10]. Recently, Zhou and colleagues achieved a significant breakthrough in this area by successfully developing the RV32-WUJI, a RISC-V 32-bit microprocessor based on 5900 molybdenum disulfide (MoS₂) transistors, demonstrating the great potential of 2D semiconductors in complex circuits. This microprocessor achieved a manufacturing yield of 99.77% and a low power consumption of 0.43 mW at an operating frequency of 1 kHz, showcasing the feasibility and efficiency of 2D semiconductor technology in practical applications (Nat. (2025).

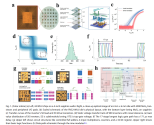

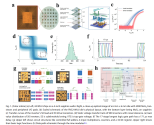

In the manufacturing process, the researchers use a 4-inch MoS₂ wafer to successfully fabricate the RV32-WUJI microprocessor. The microprocessor employs a top-gate field-effect transistor (FET) structure that is compatible with mainstream silicon CMOS technology[12]. The manufacturing process includes front-end-of-line (FEOL) and back-end-of-line (BEOL) processes. By employing a systematic co-optimization strategy and machine learning to analyze the impact of each process step on device performance, the researchers achieve a high yield (99.92% for transistors) and low power consumption (0.43 milliwatts at 1 kHz) in the wafer-scale 2D integrated circuit manufacturing. Fig. 1(a) presents the optical microscopic images of the entire wafer and a single RV32-WUJI chip, highlighting the complexity and scale of the manufacturing. Fig. 1(b) clearly illustrates the four-layer structure of the microprocessor, including the source and drain layer (M0), gate layer, logic connection layer (M1), and module connection layers (M2 and M3), clarifying the functions and interconnections of each layer. This four-layer structure is crucial for achieving the high integration density and functionality required for complex microprocessors. The use of a top-gate structure allows for better control over the electrical properties of the MoS2 transistors, which is essential for high-performance digital circuits. Additionally, the researchers optimize the process flow to ensure compatibility with existing CMOS technologies, making the integration of 2D materials more feasible.