You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Chinese semiconductor industry

- Thread starter Hendrik_2000

- Start date

- Status

- Not open for further replies.

hmm, not just Nio, but all the Chinese EV makers are doing so. And they all say 1000 TOPS is no problem.

NIO leaving Nvidia for the ET9 and moving to in-house developed Shenji chips.

However, NIO, being what it is, decided to go with a 5nm process that currently cannot be handled by SMIC. So if US govt wants to cut them off (for not buying Nvidia chips and for making AI inference chip that's too powerful), they can easily do so.

Nio bought intelligent suspension system from an American company as well. Don’t think they worry about sanctions at all.hmm, not just Nio, but all the Chinese EV makers are doing so. And they all say 1000 TOPS is no problem.

However, NIO, being what it is, decided to go with a 5nm process that currently cannot be handled by SMIC. So if US govt wants to cut them off (for not buying Nvidia chips and for making AI inference chip that's too powerful), they can easily do so.

I think you've got the small core and mid-core mixed up.These are the cores used in the K9000S:

2.62 (TaiShanV120)

2.15 (TaiShanV120)

1.53 (Cortex-A510)

My guess is this K9000SL is a 2.35 GHz TaiShanV120 core with SMT turned on, with another three 2.15 GHz TaishanV120 cores with SMT turned off, and four 1.53 GHz Cortex-A510 cores.

Take a second look at the screen shot, it lists:

| K9000SL | K9000S | |

| Large core | 2 x 2350MHz. Likely SMT. | 2 x 2620MHz. SMT. |

| Mid core | 4 x 2150MHz. Likely SMT. | 6 x 2150MHz. SMT. |

| Small core | 3 x 1530MHz. No SMT. | 4 x 1530MHz. No SMT. |

| Total | 6 SMT cores + 3 non-SMT = 6-core processor, 9 threads. | 8 SMT cores + 4 non-SMT = 8-core processor, 12 threads. |

Based on my understanding, the main difference with K9000S is that(1) the big core frequency is lower, (2) one mid-core was cut, (3) one small-core was cut.

Did you look at the picture in the X/Twitter post? It has four small cores.I think you've got the small core and mid-core mixed up.

Take a second look at the screen shot, it lists:

K9000SL K9000S Large core 2 x 2350MHz. Likely SMT. 2 x 2620MHz. SMT. Mid core 4 x 2150MHz. Likely SMT. 6 x 2150MHz. SMT. Small core 3 x 1530MHz. No SMT. 4 x 1530MHz. No SMT. Total 6 SMT cores + 3 non-SMT = 6-core processor, 9 threads. 8 SMT cores + 4 non-SMT = 8-core processor, 12 threads.

Based on my understanding, the main difference with K9000S is that(1) the big core frequency is lower, (2) one mid-core was cut, (3) one small-core was cut.

you are wrong. Please look over the post again. The only differences are what @gelgoog pointed outI think you've got the small core and mid-core mixed up.

Take a second look at the screen shot, it lists:

K9000SL K9000S Large core 2 x 2350MHz. Likely SMT. 2 x 2620MHz. SMT. Mid core 4 x 2150MHz. Likely SMT. 6 x 2150MHz. SMT. Small core 3 x 1530MHz. No SMT. 4 x 1530MHz. No SMT. Total 6 SMT cores + 3 non-SMT = 6-core processor, 9 threads. 8 SMT cores + 4 non-SMT = 8-core processor, 12 threads.

Based on my understanding, the main difference with K9000S is that(1) the big core frequency is lower, (2) one mid-core was cut, (3) one small-core was cut.

Did you look at the picture in the X/Twitter post? It has four small cores.

What I see in the Twitter picture is the K9000SL has three cores with a frequency of 1530MHzyou are wrong. Please look over the post again. The only differences are what @gelgoog pointed out

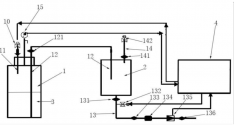

Jinghe Integrated disclosed the patent of photoresist conveying device to prevent photoresist from crystallizing due to slow flow rate.

According to the announcement of the State Intellectual Property Office, Hefei Jinghe Integrated Circuit Co., Ltd. has disclosed a patent called "A photoresist conveying device", the authorization announcement number is CN220215547U, and the application date is June 2023. .

The patent abstract shows that the utility model provides a photoresist conveying device, which includes a first container, a second container, a first pipeline, a second pipeline and a third pipeline; the first container is used to store photoresist; The first pipeline is used to transport gas into the first container, the output port of the first pipeline is connected to the first container, and the output port of the first pipeline is located close to the top of the first container; the input port of the second pipeline Connected to the first container, the output port of the second pipeline is connected to the second container, and the input port of the second pipeline is located close to the bottom of the first container; the input port of the third pipeline is connected to the glue outlet of the second container Connected to output the photoresist transported into the second container, and the glue outlet is provided at the bottom of the second container. The photoresist transport device uses a pneumatic structure to transport the photoresist to prevent the photoresist from crystallizing due to slow flow rate, and uses the second container as a buffer container to avoid the waste of photoresist during the replacement of the photoresist container.

- Status

- Not open for further replies.