You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Chinese semiconductor industry

- Thread starter Hendrik_2000

- Start date

- Status

- Not open for further replies.

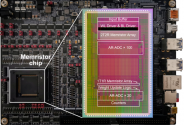

Gao Bin’s research group at the School of Integrated Circuits at Tsinghua University has made a major breakthrough in the field of memristor storage and calculation integrated chips that support on-chip learning.

Artificial intelligence technology supported by large computing power has greatly changed human production and lifestyle. However, the subsequent massive parameters have caused the demand for computing power to continue to rise. How to solve the huge computing power gap and achieve a substantial improvement in energy efficiency ratio is becoming increasingly urgent. As the specific carrier of computing power, high-computing power and high-energy-efficiency chips have become the core base that drives the development of this round of intelligent revolution, and are also the source of power that promotes the continuous development of human society.Faced with the major challenge of the traditional separation of storage and calculation architecture that restricts the improvement of computing power, Professor Wu Huaqiang and Associate Professor Gao Bin of the School of Integrated Circuits focused on the research of integrated memory and calculation technology of memristor to explore and realize a new paradigm of computer systems. The integrated memory and computing technology of memristor has completely subverted the traditional von Neumann computing architecture from the underlying devices, circuit architecture and computing theory, and can achieve a leap-forward improvement in computing power and energy efficiency. At the same time, this technology can also take advantage of the learning of the underlying devices. Features support real-time on-chip learning and enable new edge training scenarios based on local learning.

Current international relevant research mainly focuses on the demonstration of learning functions at the memristor array level. However, the realization of a fully system-integrated memristor chip that supports efficient on-chip learning still faces great challenges and has not yet been achieved, mainly due to traditional The high-precision weight update method required by the backpropagation training algorithm has poor adaptability to the actual characteristics of the memristor. Specifically, firstly, due to the inherent non-ideal characteristics of memristor, to accurately update the weight, the memristor needs to be repeatedly verified and programmed, resulting in a large amount of power consumption and delay; secondly, during the weight update process, it is necessary to Different memristors impose different operating conditions, making it difficult to implement an efficient parallel conductance modulation strategy; third, the high-precision weight update calculation results in excessive overhead.

In order to solve the above problems, based on the integrated storage and calculation computing paradigm, the research team creatively proposed a new general algorithm and architecture (STELLAR) that adapts the memory and calculation integration of memristors to achieve efficient on-chip learning, effectively realizing large-scale analog memristor arrays and CMOS Through single-chip three-dimensional integration, through the whole-process collaborative innovation of algorithms, architecture, and integration methods, the world's first fully system-integrated memristor storage and computing integrated chip that supports efficient on-chip learning was developed. The chip contains all circuit modules necessary to support complete on-chip learning, successfully completed multiple on-chip incremental learning function verifications, demonstrated high adaptability, high energy efficiency, high versatility, high accuracy and other characteristics, effectively strengthening the application of smart devices in The ability to learn and adapt in actual application scenarios provides an innovative development path to break through the energy efficiency bottleneck under the traditional von Neumann computing architecture.

when i read this it made me laugh... they are like a kid whose toy is taken away from them

View attachment 118788

US thought semiconductors was their ‘nuclear option’ to strangle China’s technology development and played this card. With the emergence of 5G Mate 60 phone, they are in complete disbelief. This is why they are in complete panic. Scrambled minds. Once the semiconductor industry has been conquered, there isn’t many other industries that they can block to stifle China’s development because China is self-sufficient in most other industries. I think maybe only commercial aviation is the major industry where the West still has a big advantage in.

He's pretty positive on China will be the 1st country to master, introduce and commercialize next-gen lithography, i.e. XRL to succeed the EUVs of today, though.

Dude is duious that SSMB-EUV can work, and he is really positive on Chinese semiconductor development.

How different is the XRL compared to SSMB-EUV? Do they belong to the same category in the first place and/or shares many commonalities?

Back in May, CEC (who founded Phytium) & Huawei formed the Pengteng ecosystem to promote ARM in China I think.

Recently, a 2023 world computing conference was hosted in Changsha, Hunan

Progress on Pengteng ecosystem project was discussed, centering around using Kunpeng & Phytium computational platform for different industries

Recently, a 2023 world computing conference was hosted in Changsha, Hunan

Progress on Pengteng ecosystem project was discussed, centering around using Kunpeng & Phytium computational platform for different industries

when i read this it made me laugh... they are like a kid whose toy is taken away from them

View attachment 118788

They are wasting so much time and money to develop, investigate, and enforce these ever growing sanctions.

Instead they should be putting this money into things like R&D

when i read this it made me laugh... they are like a kid whose toy is taken away from them

View attachment 118788

How would they enforce those criminal charges? As Meng Wangzhou once said: “fool me once, shame on you. Fool me — you can’t fool me again”.

haha... they're going to ban IP... chip making materials for SMIC and....they're crazyHow would they enforce those criminal charges? As Meng Wangzhou once said: “fool me once, shame on you. Fool me — you can’t fool me again”.

If they dare to do anything to Honor... I don't believe China will treat Iphone well

Total investment is 920 million! Provide 450 jobs! A major project in Gaoqing starts construction

Shandong Qifu New Materials' fluorine-containing high-end electronic materials project is located in Gaoqing County Chemical Industrial Park. The first phase covers an area of 209 acres, with a total investment of 920 million yuan, a total construction area of 72,000 square meters, and the construction of 40,000 tons/year difluorochloromethane (R22), 20,000 tons/year tetrafluoroethylene (TFE), 10,000 tons/year hexafluoropropylene (HFP), 2,000 tons/year octafluorocyclobutane (C4F8), 3,000 tons/year fusible polytetrafluoroethylene (PFA), 3,000 tons/year polyperfluoroethylene-propylene (FEP), and 50,000 tons/year methyl chloride (R40) production lines.

Project Highlights

Fluorine-containing polymer materials are in the high-end field of the fluorine chemical industry. They have excellent properties such as heat resistance, chemical corrosion resistance, high light transmittance, and low friction. They are widely used in automobiles, chemicals, electronics, engineering and other fields. They are It is one of the fastest growing and most promising industries in the fluorine chemical industry chain. Benefiting from the increased demand driven by the rapid development of downstream industries such as high-end equipment manufacturing, new energy, and electronic information, my country's demand for fluorine-containing polymer materials will further increase. After the project is completed, it will be able to achieve 3,000 tons/year high-purity PFA and 3,000 tons/year FEP production capacity, breaking the foreign monopoly restrictions on high-purity PFA and other fluorine-containing polymer materials, getting rid of the "stuck" state of my country's electronic materials, and quickly realizing localization. substitute. The project construction period is from September 2023 to August 2024. After the project reaches full production, it is expected to achieve annual operating income of 3 billion yuan, annual profit of 400 million yuan, total tax contribution of over 180 million yuan, and provide approximately 450 local jobs. The project will become a new engine for county economic development and enhance the development pattern of the fluorine materials industry.

SSMB should be able to be used for X-ray lithography as well, but the main problem boils down to photoresists than the actual scanners.He's pretty positive on China will be the 1st country to master, introduce and commercialize next-gen lithography, i.e. XRL to succeed the EUVs of today, though.

How different is the XRL compared to SSMB-EUV? Do they belong to the same category in the first place and/or shares many commonalities?

- Status

- Not open for further replies.