3D Heterogeneous System Integration - Technological Innovation Leads the Era of Chip Performance

On July 5 , 2022 , by the Jinji Lake in Suzhou, at the " 10th Crystal Core Seminar -- Expanding Moore's Law : Synergistic Development Conference of Advanced Semiconductor Manufacturing and Packaging Technology " hosted by "Semiconductor Core Technology" magazine , Mr. Hong Qiyuan, Senior Vice President of SIMM Technology, gave a speech titled " Three-Dimensional Heterogeneous System Integration - Technology Innovation Leads the Era of Chip Performance". In his speech, Mr. Hong introduced the latest progress of SIMM Technology, HITOC™ technology and its 3D heterogeneous system integration business to the guests .

Simmon 's unique HITOC™ technology

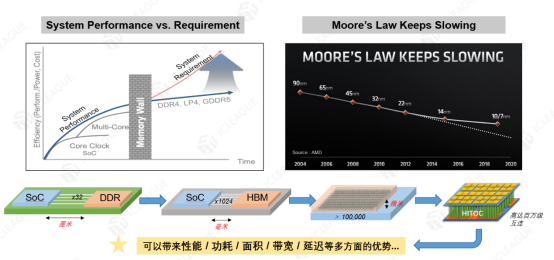

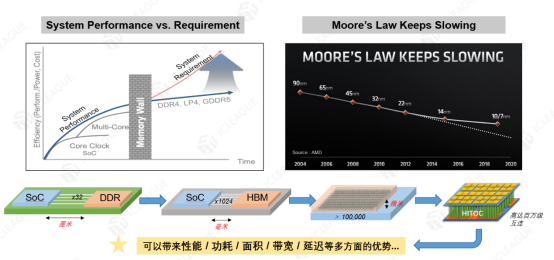

In recent years, with the technical and cost constraints of the development of integrated circuits in various dimensions , the road along Moore's Law has become more and more rugged, and the frequency and performance of CPUs have become smaller . Advanced process node stepping. The memory wall , power consumption wall, and the limitations of advanced technology are becoming more and more pain points. The unique HITOC™ ( Heterogeneous Integration Technology on Chip ) technology of SIMM Technology enables Moore's Law to continue in the three-dimensional structure, thus leading the new track of three-dimensional chips .

Chipmonitor's HITOC™ technology is different from traditional advanced packaging. It uses advanced hybrid bonding (Hybrid bonding) integrated circuit manufacturing technology to integrate chips of different types , structures and even different process nodes . The most typical application scenario is to integrate the multi-functional SOC chip and the distributed DRAM chip into an ultra-high-performance single-chip . Compared with the traditional SOC with external DDR and the use of HBM-based 2.5D advanced packaging, HITOC™ technology greatly improves the performance. The density and number of connections are increased, the PHY interface is omitted, and the length of connections is greatly shortened, which can significantly reduce system power consumption and area, greatly improve storage bandwidth, and then break through memory bottlenecks, greatly enhancing the overall computing performance of the chip system. .

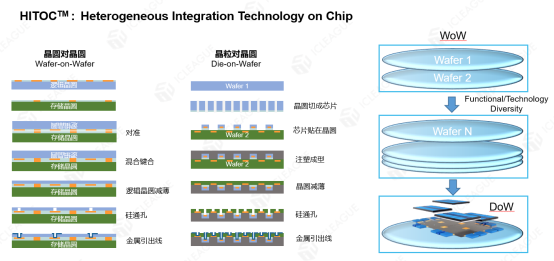

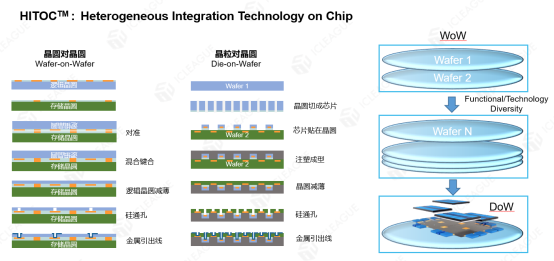

HITOC™ technology mainly includes two technical routes: Wafer-on-Wafer (wafer-to-wafer) and Die-on-Wafer (chip-to-wafer) .

Taking logic wafer to DRAM wafer as an example, after the integration of chip design and process, the logic wafer and DRAM wafer are connected together by Hybrid Bonding, and then thinned to make through -silicon vias. After the metal is drawn out and then cut and packaged, it is no different from a single chip. The chip-to-wafer technology realizes a high-performance complex chip system by bonding and stacking different chips selected by cutting and stacking on another wafer , and then through injection molding, thinning, TSV, metal wire extraction and other processes . Wafer-to-wafer technology chip products are very mature and are already in mass production. The research and development of multi- wafer-to-wafer and chip-to-wafer stacking technologies will also be basically completed by the end of this year.

As early as September 2020, SIMM Technology released the world's first high-performance AI chip based on HITOC™ architecture - SUNRISE, which has been successfully applied in the field of intelligent defect classification systems for fab production lines. At the China International Semiconductor Technology Conference (CSTIC) 2022 in June this year, Dr. Hong Feng, CEO of Corecom Technology, released the world's first VCAT 3D 4F² DRAM architecture based on HITOC™ technology. It can be seen that Chip Union Technology has innovatively used HITOC™ technology in multiple application dimensions to lead the transformation of chip products to a true three-dimensional architecture.

SIMM Technology 's 3D Heterogeneous System Integration Business

Three-dimensional heterogeneous system integration is a core business of SIMM Technology, which aims to provide customers with a complete set of three-dimensional heterogeneous system integration services in the fields of large computing power, high bandwidth, and low power consumption to enhance product value.

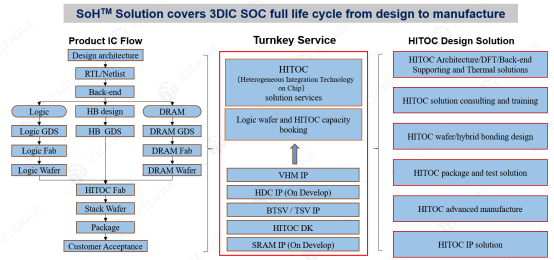

Simmon 's SOH™ ( System On HITOC ™ ) system integration solution can cover the entire process from chip design to mass production to help customers complete 3D heterogeneous integrated chip design and system integration , including the integration of heterogeneous integration technologies. Design consulting services, chip architecture /DFT/ mid-end and back-end solutions based on heterogeneous integration technologies, wafer / chip-level hybrid bonding design and manufacturing solutions , and related IP development and licensing business.

Refer to the figure above to take the three-dimensional integration of Logic + DRAM as an example:

From the chip design architecture, to the RTL, Netlist and back - end design startup , the design of Logic , DRAM , and hybrid bonding and the generation of GDS, to Logic and DRAM F ab , to Hybrid Bonding F ab Bonding production, final package testing and delivery to customers for acceptance. During the whole process, SIMM Technology can provide customers with a complete set of integrated design services based on HITOC ™ technology , including chip architecture, design, testability, back-end services and thermal simulation model solutions ; Hybrid bonding design and manufacturing solutions between multiple wafers , HITOC ™ system package test, advanced manufacturing and design consulting and training services. Of course, Simmons can also provide design services, capacity reservations and related tape-out services for Logic + DRAM , Logic + Logic and Logic + SRAM products in different stacking forms .

As an important part of 3D chips , Simmons can also provide related IP development and licensing services , such as VHM (Versatile HITOC ™ Memory) , HDC ( HITOC ™ DRAM Controller ) and Backside TSV , TSV , SRAM, etc. The three-dimensionalization of IP and other more heavyweight IPs is underway at the same time , and will be provided to customers one after another.

Simmons' 3D heterogeneous system integration industry ecology is very mature, and can provide customers with mature HITOC ™ 3D Design Kit , Work Flow , methodology and reference design documents. Simmons has mature and stable hybrid bonding Fab resources , as well as logic wafers and specially customizable DRAM wafer resources to meet customers' various needs from engineering verification of 3D chip architecture to mass production .

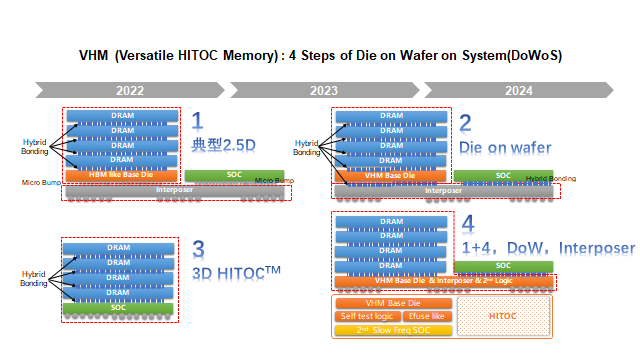

In addition to 3D solutions, Microcomm can also provide customers with 2.5D solutions based on VHM ( Versatile HITOC ™ Memory ) technology . Referring to the figure above, its cooperable product forms are very flexible, including:

1. HBM Like high bandwidth DRAM solution (can replace HBM and have more bandwidth and cost advantages);

2.Process in Memory solution (provides standard Memory interface, customers can customize the acceleration logic in Memory);

3.Custom SOC solution (as a co-processor and SOC packaged together to provide additional high computing power features);

4.eDRAM solution (provides a high-density high-speed storage between Last Level Cache and Main Memory).

Chipmone has successfully cooperated with a number of high-quality customers in the 3D heterogeneous system integration business. Taking Haowei Technology, a leading high-performance computing chip manufacturer , as an example, it has jointly developed with Chipmone Technology based on HITOC™ technology and will tape out in 2021 . On the successful cuckoo 2 chip, a large-capacity storage-computing integrated 3D architecture has been innovatively realized. The chip area of Cuckoo 2 reaches 800 ² . It includes multi-core, heterogeneous computing cores , Intelligent-NOC on-chip network, and a three-dimensional storage unit composed of distributed SRAM and high-bandwidth and low-latency DRAM . Its on-chip storage capacity Up to 6GBytes, memory bandwidth up to 6TB/s. A leap in performance compared to traditional architecture counterparts on the market .