A Sige Channel Gate-All-Around Transistor Fabricated Using Novel Cyclic Self-Limiting Wet Etching Combined with SI Removal Process.

Institute of Microelectronics

Abstract:

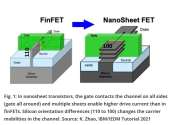

In this work, a novel SiGe channel gate-all-around (GAA) transistor using a cyclic self-limiting wet etching process combined with Si removal process after dummy gate removal in the mainstream FinFET process is demonstrated in detail. The width of SiGe channel is narrowed from 20 nm to 6.5 nm and its mole fraction of Ge of SiGe channel can be increased from 31.8% to ~40%. Meanwhile, IDS of 382 μA/μm is obtained at VDS = VGS = -0.8V, with ION/IOFF ratio of ~5.5e5 and SS of 76 mV/dec. These results prove that this novel process provides a potential solution to prepare the SiGe channel GAA transistor.