You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Chinese semiconductor thread II

- Thread starter vincent

- Start date

With a total investment of 3.5 billion yuan, Qingyi Optoelectronics Foshan mask production base started construction

the groundbreaking ceremony of the construction project of Shenzhen Qingyi Optoelectronics Co., Ltd. (hereinafter referred to as "Qingyi Optoelectronics") "Flat Panel Display and Semiconductor Mask" production base (Nanhai, Foshan) was held in Nanhai Dan Stove held.

It is reported that the overall investment in the project is about 3.5 billion yuan, and the construction content includes a mask production line for flat panel displays and a mask production line for semiconductor ICs. With an annual output of 80,000 photomasks, we can achieve mass production of 250-28nm photomasks, meeting the mask needs of 8-inch and 12-inch wafer fabs.

Qingyi Optoelectronics has been focusing on the R&D, design, production and sales of masks since its establishment in 1997. It is China's leading mask company mainly engaged in R&D, production and sales of flat panel display and semiconductor masks. , and is also one of the largest flat panel display mask companies in China.

Foshan investment news shows that the fixed asset investment in this project is approximately 1.8 billion yuan, and the fixed asset investment data per mu has set the highest intensity of fixed asset investment in industrial investment projects in Foshan, effectively filling the industrial gap in the semiconductor photomask field in Foshan Nanhai.

It is reported that in December 2023, Qingyi Optoelectronics signed a cooperation agreement with the People's Government of Nanhai District, Foshan City, Guangdong Province to invest in the construction of a Foshan production base project. The project includes a high-precision mask production base construction project and a high-end semiconductor mask production base. construction project.

It is reported that the overall investment in the project is about 3.5 billion yuan, and the construction content includes a mask production line for flat panel displays and a mask production line for semiconductor ICs. With an annual output of 80,000 photomasks, we can achieve mass production of 250-28nm photomasks, meeting the mask needs of 8-inch and 12-inch wafer fabs.

Qingyi Optoelectronics has been focusing on the R&D, design, production and sales of masks since its establishment in 1997. It is China's leading mask company mainly engaged in R&D, production and sales of flat panel display and semiconductor masks. , and is also one of the largest flat panel display mask companies in China.

Foshan investment news shows that the fixed asset investment in this project is approximately 1.8 billion yuan, and the fixed asset investment data per mu has set the highest intensity of fixed asset investment in industrial investment projects in Foshan, effectively filling the industrial gap in the semiconductor photomask field in Foshan Nanhai.

It is reported that in December 2023, Qingyi Optoelectronics signed a cooperation agreement with the People's Government of Nanhai District, Foshan City, Guangdong Province to invest in the construction of a Foshan production base project. The project includes a high-precision mask production base construction project and a high-end semiconductor mask production base. construction project.

SCAPSM: attenuated phase-shift mask structure for EUV lithography

EDA Center, Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China

University of Chinese Academy of Sciences, Beijing 100049, China

Guangdong Greater Bay Area Applied Research Institute of Integrated Circuit and Systems, Guangzhou 510700, China

Abstract

The attenuated phase-shift mask (Att. PSM) is proven to be a promising resolution enhancement technology (RET) to improve the imaging performance in extreme ultraviolet (EUV) lithography. However, due to the reflective nature of the mask structure, the serious shadowing effect can affect the diffraction near field of the mask intensely and further impact the lithography imaging. With the purpose of improving the contrast of lithography imaging, a novel structure of the Att. PSM, to the best of our knowledge, is proposed in this paper. By introducing an absorbent sidewall along the edge of the mask absorber, the diffraction and shadowing effects can be mitigated. By applying the Kirchhoff approximation of mask diffraction, the ability of the novel structure to improve imaging performance is theoretically analyzed. Additionally, these analyses are confirmed by rigorous lithography simulations. The simulation results demonstrate that the proposed mask structure can improve the imaging contrast of EUV lithography, which has potential usage in advanced integrated circuit (IC) manufacturing.

Fortune Precision going beyond components and getting on Semiconductor Equipment Modules.

Modular procurement is expected to become a future trend for domestic equipment manufacturers, and the company's module revenue is expected to continue its high growth in 2024. In the past few years, domestic equipment manufacturers mainly focused on the design of complete machines, and their modular design capabilities were weak, so they mainly focused on purchasing parts. As domestic equipment manufacturers improve their modular design capabilities, the demand for modular procurement is expected to continue to increase, and gas cabinets The market for Gas-Box products will unleash huge growth. The company's products are optimized from single-piece customization to modularization. Modular products include gas cabinet modules, ion implanter modules, etched valve body modules, transition cavity and transmission cavity modules, etc., 23H1 modules and gas pipes Road product revenue increased by 95% year-on-year, and the growth rate was significantly higher than the overall revenue growth rate of 38.6% in 23H1. The company's Nantong plant production capacity will be gradually released from 2024 to 2025. Of the designed annual production capacity of 2 billion yuan, process parts, structural parts, module products, and gas pipelines are expected to be 280, 72, 84, and 160 million yuan respectively, of which Module products account for the highest proportion. According to the company's guidance, the revenue growth rate of module products in 2024 is expected to be higher than the growth rate of the parts business, and the proportion will continue to increase in the future.

proelite

Junior Member

Protectionism.

Luckily, the world minus the EU and US markets are enough.

Exactly. The little semiconductor industry Europe has left is basically these "legacy" chips. Like the ones made by STMicro and NXP.Protectionism.

Luckily, the world minus the EU and US markets are enough.

The exact kinds of chips you would use for either legacy automotive or consumer appliances.

These European companies have plenty of Chinese competitors today like GigaDevice and others. If you look at the current Chinese "legacy" chips portfolio it has replacements for basically all the European chips.

Chinese chip makers are much further behind with making alternative designs for US "legacy" chips like the mixed-signal ones by Analog Devices or TI.

Last edited:

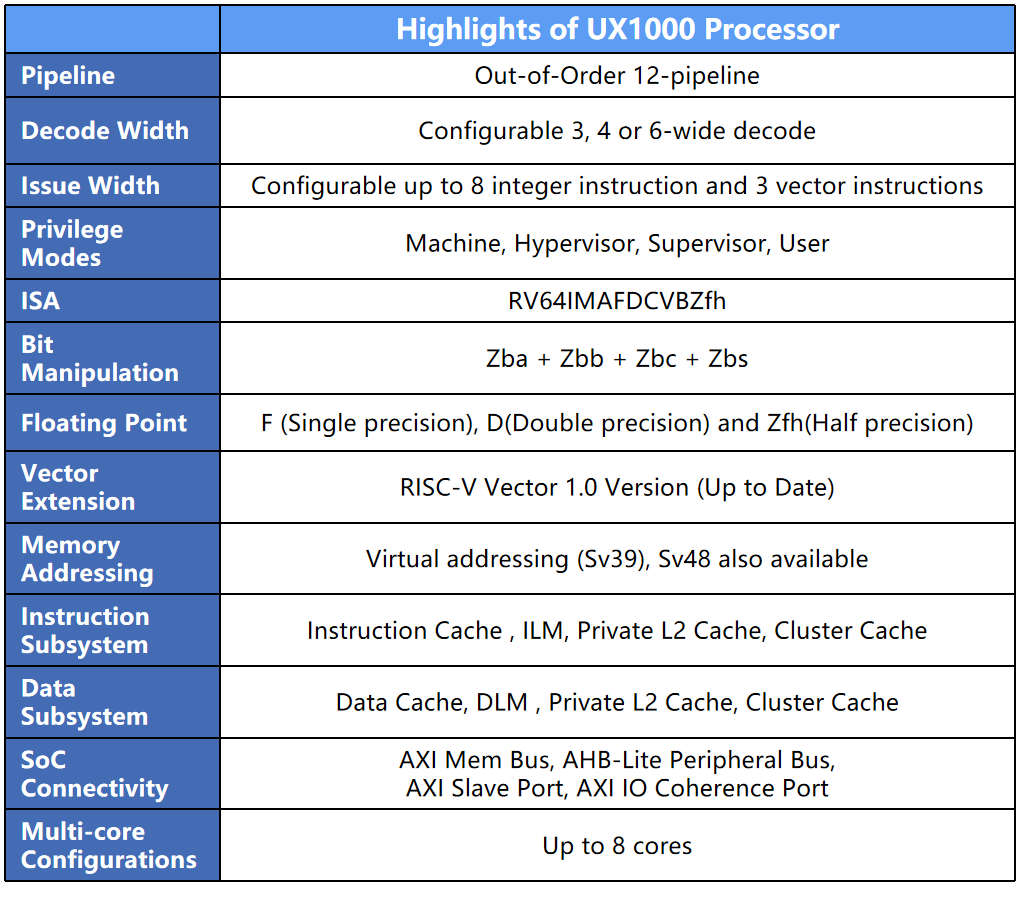

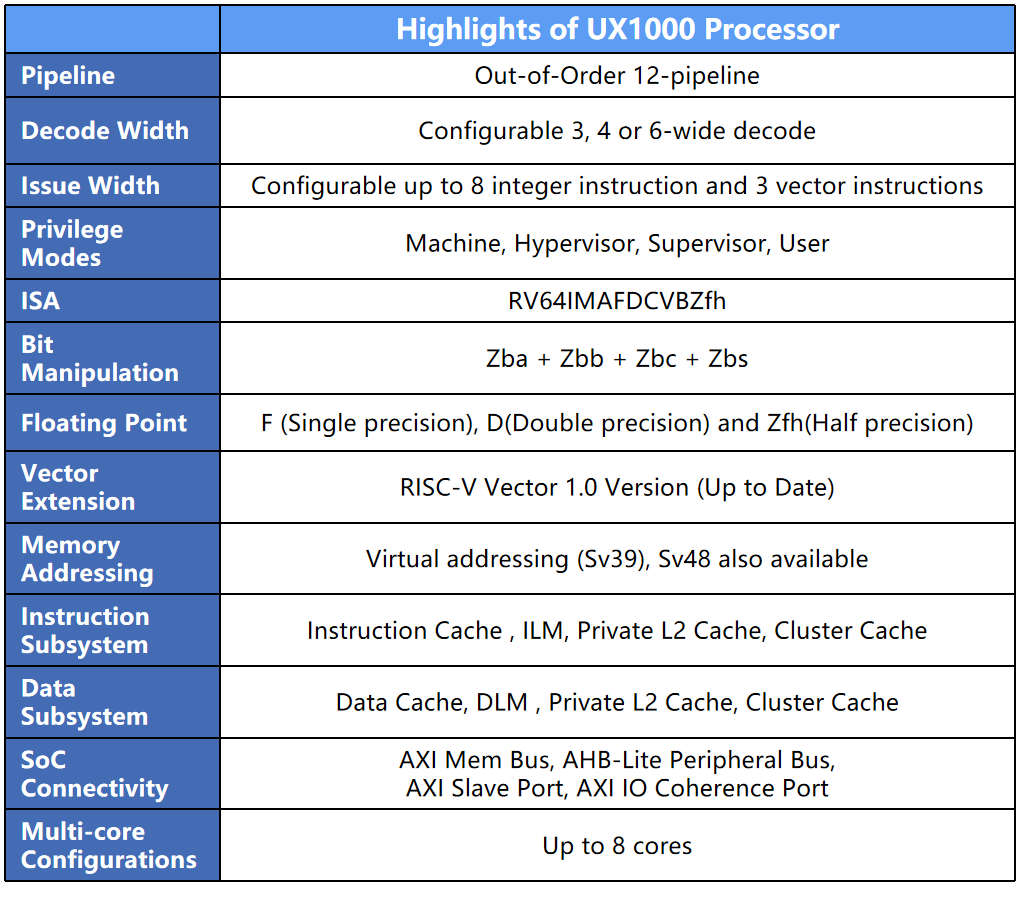

Nucleisys releases the 1000 series cores, opening a new chapter of out-of-order high performance

2024-03-18

Nucleisys, a local leader in RISC-V CPU IP, officially released the UX1000 series, a high-performance commercial processor CPU IP based on the RISC-V instruction set, providing domestically produced RISC-V CPU IP for high-performance processor cores.

...

The newly released UX1000 series by Nucleisys is a 64-bit high-performance application processor with multiple decoding widths, out-of-order launch and execution capabilities. It is mainly targeted at network processing, artificial intelligence, autonomous driving, data center accelerator cards, and high-performance applications such as mobile devices which further meet the growing local demand for domestically produced high-performance processor IP.

The UX1000 series has a highly configurable pipeline that users can customize based on different performance requirements, providing strong flexibility in system design:

The UX1000 series is available in three different configuration categories: UX1030, UX1040 and UX1060

UX1030: 3 decoding width processor

Single core features

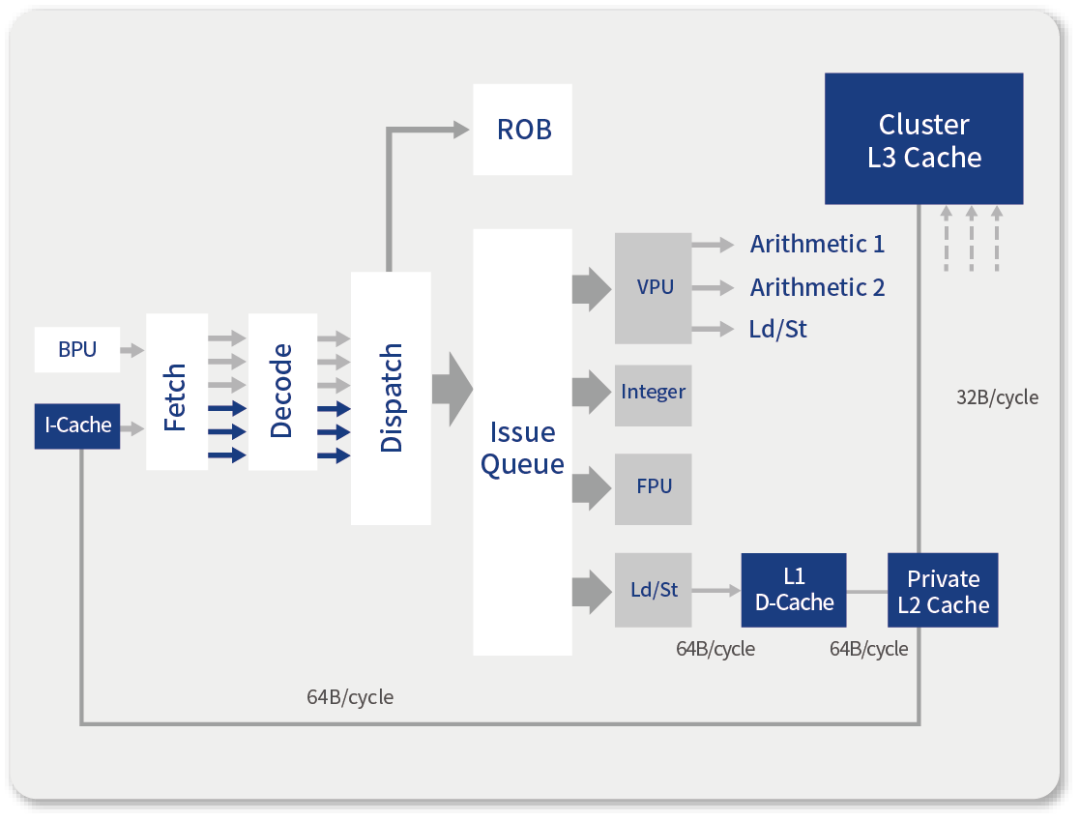

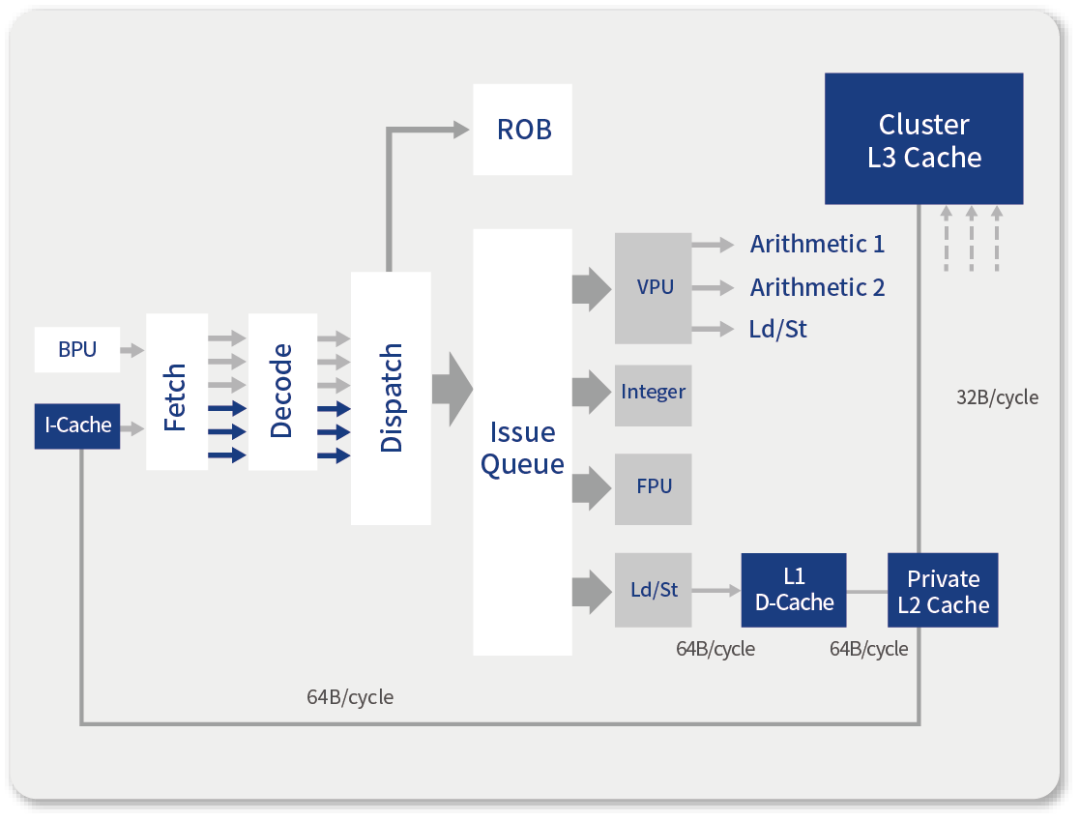

The UX1000 series processor is a 12-stage pipeline out-of-order execution processor based on RISC-V RV64IMAFDCVBKZfh and strictly follows RISC-V standard instructions;

UX1000 has strong computing power and supports issue width (Issue Width) of up to 10 scalar instructions and 2 vector instructions per cycle;

Configurable instruction and data cache (ICache / DCache) and on-chip SRAM (ILM / DLM) and supports ECC;

In terms of memory access design, UX1000 supports private L2 cache, providing more efficient data reading and storage capabilities;

Supports the VPU vector computing unit that strictly follows the RISC-V Vector 1.0 standard. It has 2 computing pipeline units and 1 data reading and writing pipeline. It can be configured with 128b/256b VLEN and supports INT8/16/32/64 and BF16/F16. /F32/F64 data type.

Multi-core configurable features

Supports up to one Cluster 8 cores and cache consistency;

Configurable private L2 and Cluster Cache;

Configurable IO consistency interface (IOCP). With the help of IOCP interface, external devices (such as NPU, accelerator, PCIe, DMA, etc.) can share data reading with Core and Cluster cache and maintain cache consistency;

Cluster Cache supports SECDED ECC;

Supports configuring Cluster Cache as Cluster Local Memory and can support CLM interface.

...

2024-03-18

Nucleisys, a local leader in RISC-V CPU IP, officially released the UX1000 series, a high-performance commercial processor CPU IP based on the RISC-V instruction set, providing domestically produced RISC-V CPU IP for high-performance processor cores.

...

The newly released UX1000 series by Nucleisys is a 64-bit high-performance application processor with multiple decoding widths, out-of-order launch and execution capabilities. It is mainly targeted at network processing, artificial intelligence, autonomous driving, data center accelerator cards, and high-performance applications such as mobile devices which further meet the growing local demand for domestically produced high-performance processor IP.

The UX1000 series has a highly configurable pipeline that users can customize based on different performance requirements, providing strong flexibility in system design:

The UX1000 series is available in three different configuration categories: UX1030, UX1040 and UX1060

UX1030: 3 decoding width processor

- Has better performance and lower area power consumption

- Has high performance and excellent area and power consumption

- Has higher performance, mainly for high-performance applications

Single core features

The UX1000 series processor is a 12-stage pipeline out-of-order execution processor based on RISC-V RV64IMAFDCVBKZfh and strictly follows RISC-V standard instructions;

UX1000 has strong computing power and supports issue width (Issue Width) of up to 10 scalar instructions and 2 vector instructions per cycle;

Configurable instruction and data cache (ICache / DCache) and on-chip SRAM (ILM / DLM) and supports ECC;

In terms of memory access design, UX1000 supports private L2 cache, providing more efficient data reading and storage capabilities;

Supports the VPU vector computing unit that strictly follows the RISC-V Vector 1.0 standard. It has 2 computing pipeline units and 1 data reading and writing pipeline. It can be configured with 128b/256b VLEN and supports INT8/16/32/64 and BF16/F16. /F32/F64 data type.

Multi-core configurable features

Supports up to one Cluster 8 cores and cache consistency;

Configurable private L2 and Cluster Cache;

Configurable IO consistency interface (IOCP). With the help of IOCP interface, external devices (such as NPU, accelerator, PCIe, DMA, etc.) can share data reading with Core and Cluster cache and maintain cache consistency;

Cluster Cache supports SECDED ECC;

Supports configuring Cluster Cache as Cluster Local Memory and can support CLM interface.

...