Silergy showcased its digital EDA solutions at the 2025 China International Import Expo, empowering industrial innovation.

At the 2025 China International Import Expo, Sirchip's booth in the Lingang exhibition area received numerous visitors. As a representative company in the digital EDA field, Sirchip showcased a series of cutting-edge technologies and innovative achievements in chip design verification, attracting many professional visitors from home and abroad to stop and exchange ideas.

01 Highlights of the CIIE

Silergy showcased tools for architecture design, software simulation, hardware simulation, prototype verification, and verification cloud services, demonstrating its comprehensive service capabilities for digital circuit design and implementation in fields such as artificial intelligence, high-performance computing, and image processing. Of particular note was Silergy's "ChipEye" prototype verification solution, embodying over two decades of technological accumulation. Its superior performance and continuous innovation made it an unsurprisingly popular exhibit in the area. A senior engineer from Japan stated at the event that Silergy's outstanding product capabilities and professional services are the fundamental reasons for their continued choice of the company.

View attachment 164303View attachment 164304

02 Addressing Global Chip Verification Challenges

With the rapid development of AI technology, the global integrated circuit design industry is facing unprecedented challenges. At the China International Import Expo (CIIE), a technology expert from Silergy pointed out: "The rapid development of AI applications has ushered in an era of hundreds of billions of gates in chip design, with software code volume surging to the hundreds of millions of lines, making design verification increasingly difficult." To address these challenges, Silergy has proposed three major development paths: a left-shift development strategy to provide overall solutions, in-depth cooperation with mainstream architecture and IP vendors to build an ecosystem, and the development of application-level innovative solutions adapted to emerging applications such as automotive and IoT.

View attachment 164305View attachment 164306

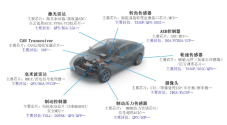

The company has already established strong partnerships with over 600 enterprises worldwide, and its products are widely used in terminal fields such as the Internet of Things, cloud computing, 5G communications, smart healthcare, and automotive electronics. Through the China International Import Expo (CIIE), Silergy has further expanded its international influence.

I don't think this is Silergy. Silergy website is here

this is 思尔芯