School of Electronics develops two-dimensional transistor with speed exceeding silicon limit

Chips provide a steady stream of power for the development of big data and artificial intelligence. The increase in chip speed is due to the miniaturization of transistors. However, the performance of traditional silicon-based field-effect transistors is gradually approaching its intrinsic physical limit. The International Roadmap for Devices and Systems (IRDS) predicts that the limit gate length of silicon-based transistors will stop at 12 nm, and the operating voltage cannot be less than 0.6 V, which defines the end of the silicon-based chip scaling process in the future Therefore, it is urgent to develop new channel materials to continue Moore's Law. Atomic-thick two-dimensional semiconductors have attracted widespread interest from both the scientific and industrial communities as one of the strong candidates for future chip channel materials due to their ultrathin body and high mobility. In recent years, the world's leading semiconductor manufacturing companies and research institutions such as Intel, TSMC, Samsung and the European Microelectronics Center have invested in research on 2D materials. However, limited by the bottlenecks of contacts, gate dielectrics, and materials, the performance of all two-dimensional transistors so far cannot match the industry's advanced silicon-based transistors, and the experimental results are far behind theoretical predictions, which are not enough to demonstrate the potential of two-dimensional semiconductors. ultimate potential.

Recently, the research team of Professor Peng Lianmao and Researcher Qiu Chenguang from the School of Electronics, Peking University has prepared a 10nm ultra-short channel ballistic two-dimensional indium selenide transistor, which for the first time made the actual performance of exceed that of Intel's commercial 10nm node silicon - based fin. Transistor, and the working voltage of the two-dimensional transistor is reduced to 0.5 V , which is also the fastest and lowest power consumption two-dimensional semiconductor transistor in the world so far . The relevant research results are titled "Ballistic two-dimensional InSe transistors", published online in Nature on March 22, 2023, web link:

-w#citeas ). Doctoral students Jiang Jianfeng and Dr. Xu Lin from the School of Electronics are the co-first authors, Professor Peng Lianmao and researcher Qiu Chenguang are the co-corresponding authors, and the School of Electronics of Peking University is the sole unit of the paper.

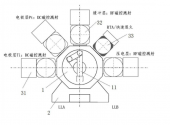

This work has achieved three technological innovations: using three layers of indium selenide with high carrier thermal velocity (smaller effective mass) as the channel, and achieving a room temperature ballistic rate as high as 83%, which is the highest value of field effect transistors at present. Much higher than the ballistic rate of silicon-based transistors (less than 60%); solved the problem of growing ultra-thin oxide layers on the surface of two-dimensional materials, prepared 2.6 nanometer ultra-thin double-gate hafnium oxide, and increased the device transconductance to 6 mS Micron, an order of magnitude more than all two-dimensional devices; pioneered doping-induced two-dimensional phase transition technology to overcome the international problem of gold-half contacts in the field of two-dimensional devices, refresh the total resistance to 124 ohm microns, and meet the requirements of future nodes of integrated circuits for transistors Resistor requirements (220 ohms • microns).

Comparing with the development roadmap of silicon-based devices predicted by the industry’s IRDS, the ballistic two-dimensional indium selenide transistor realized by the Peking University team broke the four ultimate silicon-based “red walls”: 1) The trench length was reduced to 10 nanometers (beyond silicon-based limit of 12 nm), while maintaining an ideal subthreshold swing of 75 mV range, DIBL is only 20 mV/V, and the off-state characteristics of the device exceed the best silicon-based FinFET technology. 2) The voltage is scaled down to 0.5V (beyond the 2031 silicon-based limit of 0.6V), and the device current is turned on from the standard off-state of 100nA/micron to more than 1mA/micron on-state. 3) The gate delay is reduced to 0.32 picoseconds, which is four times better than the silicon-based limit of 1.26 picoseconds. 4) The power consumption delay product is reduced to 4.32E-29JS/micron, which is an order of magnitude lower than the silicon-based limit.