When comparing our monolithic design to the chiplet MCM design, our lithography tool time increases significantly because the

has to be scanned 1.875 times. This is because a large part of the slit is not fully utilized. While there is still some efficiency in wafer loading time, most of the cost of a lithography tool is scan time. As a result, the internal cost per wafer has risen significantly.

In this hypothetical scenario, foundries now cost $2,174 more per wafer for lithography. That’s a huge cost increase that foundries won’t put up for high-volume customers who already have very tight margin deals. Assume that the foundry is priced by profit margin, so regardless of design, it can maintain a 50% gross margin.

The increased cost of underutilizing the slits in the reticle means that the foundry won’t sell these wafers for $17,000 to maintain a 50.2% gross margin. Instead, they will sell the wafers for $21,364. The cost of defect-free silicon for a monolithic product remains at $567. Instead of $215 per die, defect-free silicon costs $270. Instead of $430 per product, it’s $541.

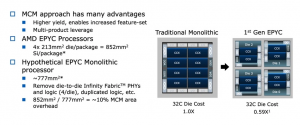

The chiplet vs monolithic decision is now more difficult. Monolithic

are likely to be cheaper to manufacture once packaging costs are factored in. Additionally, there are some power costs associated with the chiplet design. In this case, building a large monolithic chip is definitely better than using a chiplet/MCM.